CTL Redundancy

CTL Redundancy. Meeting 08-Jan-2009. Questions. Clarify RowAddressRange and ColumnAddressRange as logical or physical We need to clarify why we need each property in Redundancy block We can use relation block to define redundant units to repair pins and resources

CTL Redundancy

E N D

Presentation Transcript

CTL Redundancy Meeting 08-Jan-2009

Questions • Clarify RowAddressRange and ColumnAddressRange as logical or physical • We need to clarify why we need each property in Redundancy block • We can use relation block to define redundant units to repair pins and resources • Can we use STIL access procedure to describe serial repair load and unload or repair data • Team needs to discuss how redundancy and repair block relate to physical organization

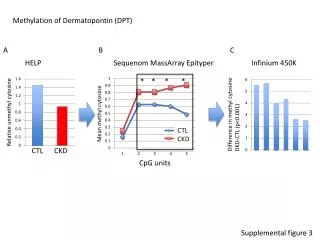

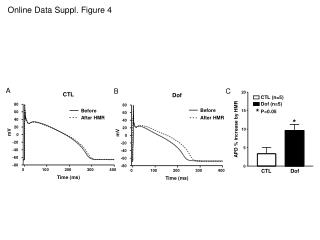

col 0 col 511 col 512 row1023 block2 block3 row 512 row 511 block0 block1 row 0 Memory Example • Memory Configuration : 32K x 32 • consists of blocks of 512 rows and 512 columns • 4 spare columns per block • Can replace a block of 4 columns • 8 spare rows per block • Can replace a block of 8 rows

CTL MemoryRepair { RedundancyElement column1 { Type Column; AccessSignals ‘REB2 + FAB2[7:0]’ Width 4 AddressMap 4n ColumnAddressRange [0..15] RowAddressRange [512 .. 1023] DataRange [0..31] } RedundancyElement column2 { Type Column; AccessSignals ‘REB0 + FAB2[7:0]’ Width 4 AddressMap 4n ColumnAddressRange [0..15] RowAddressRange [0 .. 511] DataRange [0..31] } RepairMap { } }

CTL MemoryRepair { RedundancyElement row1{ Type Row; AccessSignals ‘reb2 + fab2[6:0]’ Width 8 AddressMap 8n ColumnAddressRange [0..15] RowAddressRange [512 .. 1023] DataRange [0..31] } RedundancyElement row2 { Type row; AccessSignals ‘reb0 + fab2[6:0]’ Width 8 AddressMap 8n ColumnAddressRange [0..15] RowAddressRange [0 .. 511] DataRange [0..31] } RepairMap { } }

Memory 2 row 95 row 64 • Memory Configuration : 128 x 32 • consists of blocks of 32 rows • 2 spare rows – one each for upper and lower half row 31 row 0 row 32 row 63 row 96 row 127

CTL MemoryRepair { RedundancyElement row1{ Type Row; AccessSignals ‘reb1 + fab1[6:0]’ Width 1 AddressMap n RowAddressRange [0 .. 31, 64 .. 95] DataRange [0..31] } RedundancyElement row2 { Type row; AccessSignals ‘reb0 + fab1[6:0]’ Width 1 AddressMap n RowAddressRange [32 ..63,96 .. 127] DataRange [0..31] } RepairMap { } }

Memory Example 3 Repairable • Memory with 2 separate blocks • qa is repairable • qb is non-repairable column • Do we need port association in Redundancy element for data range? qa[3:0] qb