Overall Project Objective:

This document outlines the objectives and current progress of an innovative Radio-Frequency indoor/outdoor navigation system designed to leverage existing wireless infrastructure. Key milestones include the completion of structural and schematic designs, with significant advancement in layout and transistor counts. Major components such as the FPU and Lookup functionalities have been tested and verified. We are focused on completing global routing and finalizing interconnects to ensure project timelines align with critical milestones. Upcoming tasks include splitting schematics for LVS and addressing simulation delays.

Overall Project Objective:

E N D

Presentation Transcript

Overall Project Objective: Design a Radio-Frequency indoor/outdoor navigation system, utilizing the existing wireless infrastructure. Design Stage Objective: Final LVS and simulation RF Triangulator: Indoor/Outdoor Location Finding18-525 Architecture ProposalGiovanni FonsecaDavid FuAmir GhitiStephen RoosDesign Manager: Myron Kwai

Status Structural Verilog complete. Schematics completed. Layout of basic components complete. Major Layouts: ~90% done FPU: Done, tested. Lookup: Done, tested. Calc: interconnects. Top Three: Finishing layout: 85% done Global routing still needs to be done

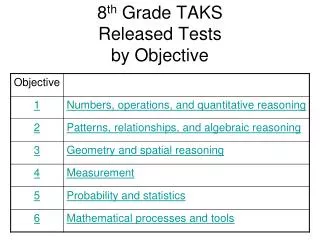

Current Transistor counts • Total: 27,150 transistors* • Top Three: 6,500 trans. 3 x FPU Add/Sub Unit 1500 trans. Control Registers & Muxes: 2000 trans. • Calc: 17,950 trans. 2 x FPU Add/Sub Unit: 1500 trans. 1 x FPU Mult/Div Unit: ~5000 trans. 1 x Logshifter: 200 trans. 1 x Comparator: 800 transistors. FSM Logic: 850 transistors 25 x 12-bit M-S En Reg: 6600 trans. total 8-1,6-1,4-1,2-1 Mux Sets: 3000 trans. total • Lookup: 2,700 trans. Control Registers & Muxes: 2000 trans. Control Logic: 163 trans. • SRAM: 12k trans * count not including SRAM, with SRAM: ~38k

FPU Layouts Multiplication & Division Layout FASU Layout

Lookup Layout Total transistor count: 15018 in layout 14851 in schematic Area = 208.8*232.3 = 48504u^2. Density: .31 transistor per u^2.

Top Three Progress Last week’s This week’s

To do • Lookup: done • FPU: done • Calc: • Finish up the interconnects. • Top Three: • Finish up the interconnects. • Split the schematics and layout into parts for LVS

Questions/Concerns • Large block simulations take a long time • Getting top3 and calc to lvs before carnival!