Core-A Processor

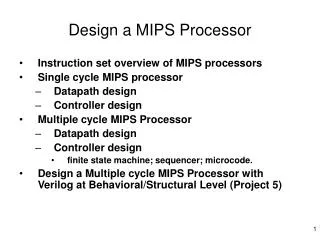

Core-A Processor. Core-A 프로세서 지원센터. Agenda. 1. Core-A Processor. 2. Cache & MMU & Debugger. 3. Core-B BUS. 4. Tool Chain & Implementation. t. 5. Core-A Homepage. Core-A System Architecture. Core-A Processor. Debugging System. External memory bus. Cache Controller. 32bit

Core-A Processor

E N D

Presentation Transcript

Core-A Processor Core-A 프로세서 지원센터

Agenda 1 Core-A Processor 2 Cache & MMU & Debugger 3 Core-B BUS 4 Tool Chain & Implementation t 5 Core-A Homepage

Core-A System Architecture Core-A Processor Debugging System External memory bus Cache Controller 32bit Processor core In-Circuit Debugger FPU DSP Memory Controller MMU High-speed bus Extended system bus Bridge User Logic SDK Peripheral bus Embedded Complier/OS Standard Peripherals AMBA IPs JTAG-Based Emulator • Platform-Based Design • Core-A System • Processor Core + Fundamental IPs + Debugger + SDK +Verification System + • Application Examples Total solution for Embedded System Design

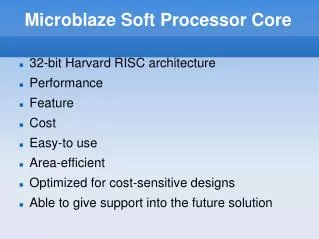

Core-A Processor IF • Core-A Processor • 32-bit RISC Processor • 5 Stage Pipeline Structure • Fully Synthesizable • Key Features • Programmable Delay • NOP Insertion before execution • Programmable Branch Slot • Powerful Load/Store Operation • LDM / STM • 32 Bit Immediate Concatenation • MUI • Extensible Architecture • Application Specific Registers • Coprocessor I/F ID EX MEM WB

Programmer Model • 16 GPR (general purpose register) • 12 general use • EPARAM (Exception parameter) • EPC (Exception PC) • RA (Return Address) • PC (program counter) • PS (program status) • 216 ASR (Application Specific Register) • CPR (Coprocessor Register)

Program / Processor Status • The high parts ([31:16]) and the low parts ([15:0]) have the same format • The high parts : the previous status before the exception • The low parts : the current status • N (Negative), Z (Zero), C (Carry), V (Overflow) • Execution result of the instruction • IE : interrupt enable – 0 for disable • M (Mode) : shows the current processor mode • 1’b0 : User Mode • 1’b1 : Supervisor Mode – protected mode for operating system for handling exception/interrupt. • ‘PS’ can be updated with MTPS/MFPS instructions

Exception & Branch • Sub-routine call • CALL/LCALL/CALLR/CALLZ/ • $RA $PC+4*n • $PC $PC+X • Return from sub-routine call • CALLR

Exception & Branch • Exception Disassembly Code 00000000 <_start>: 0: 3460001c b.al 0x1c 74 <_reset_handler> 4: 34600005 b.al 0x5 1c <_cop_handler> 8: 34600004 b.al 0x4 1c <_cop_handler> c: 34600003 b.al 0x3 1c <_cop_handler> 10: 34600004 b.al 0x4 24 <_int_handler> 14: 34600001 b.al 0x1 1c <_cop_handler> 18: 34600000 b.al 0x0 1c <_cop_handler> 0000001c <_cop_handler>: 1c: 1c6b0002 movi.al ip, 0x2 20: 420e0000 rfi 00000024 <_int_handler>: 24: 10ccffb8 addi sp, sp, -72 28: 532c0000 st.w r0, (sp + 0x0) … 68: 572c0000 ld.w r0, (sp + 0x0) 6c: 10cc0048 addi sp, sp, 72 70: 420e0000 rfi 00000074 <_reset_handler>: 74: 20002000 mui 0x2000 78: 0c6c0040 movi.al sp, concat(0x0) 7c: 42000002 ien 80: 36600004 call.al 0x4 94 <main> 84: 80000000 nop

Gated-Clock • Core-A internally uses logical clock (gated clock), not physical clock • All pipelines do not proceed if memory response is pending. nIWAIT Negative Latch Core-A Core-A gated-clock nDWAIT D Q CLK Logical Clock (Gated CLK) Physical Clock Clock Buffer

Gated-Clock Simulation Physical clock Gated logical clock nIWAIT Negative Latch nDWAIT D Q CLK Logical Clock (Gated CLK) Physical Clock Clock Buffer

Cache Controller • 4KB direct-mapped cache • 16 bytes line size / 256 sets • Support only write-back / write-allocate policy • Critical word first with wrapping burst • Coprocessor interface • Invalidate All Line • Indexed Line Invalidate • Indexed Line Clean • Indexed Line Store Tag • Indexed Line Store Data • Indexed Line Load Tag • Indexed Line Load Data

MMU • 2-level hierarchical TLB • 2-level hierarchical page table (4MB, 4KB) • Hardware-managed page table walk • Separate MMU for instruction and data memory • 16 fully-associative entries for each TLB • Controlled by CP0 • Global page support • Lockdown support • Cacheable support • Page execute protection

On-Chip Debugger • On-Chip Debugging Logic • Tightly-coupled to Core-A • Emulator Board can be replaced by • ALTERA™ Byte-blaster or XILINX™ Parallel II • SW Debugger • GDB (Ported to Core-A) • Collaborated with Core-A’s Binutils & ISS • Eclipse-based GUI Eclipse-based GUI

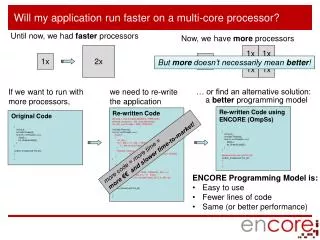

On-Chip BUS • Core-B Lite • Multiple Masters, Multiple Slaves • Pipelined Operation • Burst Transaction • Single Cycle Bus Master Handover • Non-tristate Implementation • Variable Length of Burst Transfers • Startup Address Supporting Wrapping • Load Address / Sequential Address Core-B Lite Bus Core-B Lite Arbiter Core-B Lite Master #1 C M U X Address/Control Core-B Lite Slave #1 W M U X Core-B Lite Slave #2 Core-B Lite Master #2 Write Data R M U X Read Data/Ready Core-B Lite Decoder

On-Chip BUS Core-A Processor Debugging System External memory bus Cache Controller 32bit Processor core In-Circuit Debugger DSP FPU Memory Controller MMU Core-B Lite Bus Extended system bus Core-B/APB Bridge User Logic APB Standard Peripherals AMBA IPs Bridge AHB AHB Wrapper Core-A Processor

Core-A Tool Chain • 어셈블러 및 링커 • Core-A Instruction용 바이너리 코드 생성 • 자료의존성(Data Dependency) 분석을 통한 자동 NOP 명령어 삽입 • ELF 및 Flat 파일 생성 • Link Scipt를 사용해 메모리 맵에 따라 프로그램 코드 및 데이터의 위치를 지정 • 디스어셈블러, 파일포맷 변화기 및 라이브러리 생성기 • 디스어셈블러를 통한 실행파일의 디스어셈블 기능 및 파일 포맷 변환 • 라이브러리 생성기를 이용한 라이브러리 구현 지원 • 컴파일러 • ANSI C 언어 구문 지원 • Inline Assembly Syntax 및 매크로 지원 • DWARF2 포맷 디버깅 정보 생성 • Embedded C library(newlib), uClinux의 C library(uClibc) 지원 • Floating Point 연산 지원 • 3단계의 Machine-independent 및 Machine-dependent 최적화 수행

Impelmentation • Integer Core • ASIC Implementation • Core-A, ARM : w/o cache, MMU • ARM, MIPS : w/ debugger

Core-A Homepage www.core-a.or.kr

Core-A Download Core-A 정보 -> IP 신청 및 다운로드

Core-A Download 홈페이지를 통한 Online 신청 꼭 기억하세요!!

Core-A Download 협약서 작성 및 제출

Core-A Download IP 다운로드 : 신청 아이디와 비밀번호로 조회 꼭 기억하세요!!

Core-A Download IP 다운로드 수락 여부 결과

Thank you … 설문지를 작성해 주시면 감사하겠습니다.