Układy logiczne

670 likes | 1.29k Views

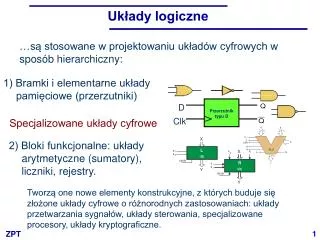

Układy logiczne. D. Przerzutnik typu D. Clk. …są stosowane w projektowaniu układów cyfrowych w sposób hierarchiczny:. 1) Bramki i elementarne układy pamięciowe (przerzutniki). Specjalizowane układy cyfrowe. 2) Bloki funkcjonalne: układy arytmetyczne (sumatory), liczniki, rejestry.

Układy logiczne

E N D

Presentation Transcript

Układy logiczne D Przerzutniktypu D Clk …są stosowane w projektowaniu układów cyfrowych w sposób hierarchiczny: 1) Bramki i elementarne układy pamięciowe (przerzutniki) Specjalizowane układy cyfrowe 2) Bloki funkcjonalne: układy arytmetyczne (sumatory), liczniki, rejestry. Tworzą one nowe elementy konstrukcyjne, z których buduje się złożone układy cyfrowe o różnorodnych zastosowaniach: układy przetwarzania sygnałów, układy sterowania, specjalizowane procesory, układy kryptograficzne. 1

74xx W latach 80…. Bloki funkcjonalne: Sumatory Liczniki Rejestry Komparatory Konwertery Bufory Rejestry przesuwajace Były produkowane w postaci katalogowych układów scalonych serii 74xx

Licznik Rejestr Mux Bloki funkcjonalne… …stanowią wyposażenie bibliotek komputerowych systemów projektowania Układ cyfrowy Każdy układ cyfrowy składamy z bloków funkcjonalnych 3

Licznik Rejestr Mux Bloki funkcjonalne… …stanowią wyposażenie bibliotek komputerowych systemów projektowania Układ cyfrowy W procesie konstruowania systemów cyfrowych struktura wewnętrzna bloku w zasadzie nas nie interesuje 4

Bloki funkcjonalne B. kombinacyjne B. sekwencyjne Pamięci Komutacyjne MUX DMUX DEC Arytmetyczne Komparator Sumator Liczniki Zliczające W górę W dół Rejestry Równoległe Przesuwające (RAM) ROM 5

Multiplekser (MUX) d N = 2n wejść informacyjnych 0 d 1 d N-1 a a n-1 0 Wejście zezwalające e y Wyjście Wejścia adresowe gdzie Pk(A) oznacza pełny iloczyn zmiennychan–1,...,a0, prostych lub zanegowanych, zgodnie z reprezentacją binarną liczby k = L(A). 6

Multiplekser (MUX) e=1 d 0 d 1 d N-1 a a n-1 0 y Dla n = 1 (MUX 2 : 1): dla n = 2 (MUX 4 : 1): dla n = 3 (MUX 8 : 1): 7

Multiplekser 4:1 d 0 =1 =0 =0 =0 d d 1 d d 2 d 3 a a 1 0 y=d0 y=d1 =0 0 =0 1 Multiplekser jako przełącznik 8

Multiplekser jako przełącznik 0 0 e 1 1 a0 a1 0 d0 d1 d2 d3 1 1 y 0 0 0 1 1 1 Każdy blok funkcjonalny można skonstruować bramek logicznych 9

Multiplekser jako przełącznik Multiplekser 11…11 00…00 Źródło danych I0 Źródło danych I 00…01 2nźródeł danych Źródło danych I1 f odbiornik 2n-1 adresów źródeł 2n-1 00…01 11…11 To nie jest połączenie w postaci ścieżki metalizowanej 10

Demultiplekser N = 2n wyjść Wejście zezwalające Wejście informacyjne Wejścia adresowe gdzie Pk(A) oznacza pełny iloczyn zmiennychan–1,...,a0, prostych lub zanegowanych, zgodnie z reprezentacją binarną liczby k = L(A). 11

Demultiplekser jako przełącznik =d =d 0 0 0 0 0 0 0 0 0 1 1 1 1 =d e a0 a1 y0 y1 0 0 y2 0 1 1 1 y3 d 12

Demultiplekser jako przełącznik 00…00 Demultiplekser f0 00…01 f1 2nodbiorników Źródło danych 11…11 f 2n-1 2nadresówodbiorników 00…01 11…11 13

Dekoder DMUX DEKODER d = 1 e = 1 N = 2n 14

Bloki komutacyjne 0 1 2 3 0 1 2 3 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 a1 a0 a1 a0 W dzisiejszych czasach można skonstruować blok komutacyjny o dowolnych wymiarach… 0 1 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 1 0 0 0 1 0 1 1 15

0 0 1 1 2 2 3 3 y 4 4 5 5 6 6 7 7 y 8 8 9 9 10 10 11 11 12 12 13 13 14 14 15 15 x3x2x1x0 MUX/DMUX w realizacji funkcji boolowskich y = (1,7,11,13,14,15) 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 x3x2x1x0 16

Bezpośrednie zastosowanie MUX/DMUX do realizacji funkcji boolowskich … należy odłożyć do kosza! Sensowne jest natomiast stosowanie tych układów do wspomagania procesu syntezy funkcji boolowskich Dobrym przykładem jest zastosowanie dekoderów do zmniejszania liczby wyjść pamięci ROM w realizacjach zespołów funkcji boolowskich. Jest to problem z zadań 11.13 i 11.14 str. 194 skryptu ULOG w zadaniach. 17

B A n n K Komparator 0001 1001 0111 0001 „1 z 3” 1 0 0 0 1 0 0 0 1 A < B A = B A > B Taki komparator można łatwo zbudować z bramek logicznych

i 3 i 2 i 1 i 0 Komparator dla liczb 4-bitowych a3 b3 a2 b2 a1 b1 a0 b0 A = a3a2a1a0 B = b3b2b1b0 A eq B = i3i2i1i0 A <B = A > B = A 1000 B 0- - - 19

Sumatory A B A n n c 0 c S n n Y Sumator – podstawowy BF powszechnie stosowany w technice DSP Inne układy arytmetyczne: układy odejmowania układy mnożące układy dzielenia ...są budowane z sumatorów 20

Najprostszy sumator B A n n a a b a b b n-1 i i 0 0 n-1 c 0 c c c c c n n 1 i+1 S i S S c S 0 c n-1 y y y n-1 i 0 n Y Jak jest zbudowane pojedyncze ogniwo? Kaskadowy – ripple carry adder 0111 1001 0110 C4=0 C4=1 0000 1111 21

Funkcje logiczne sumatora a b 0 0 c co 0 1 S 0 1 1 0 0 1 y 1 0 1 0 1 1 22

Funkcje logiczne sumatora a b 0 0 c co 0 1 S 0 1 1 0 0 1 y 1 0 1 0 1 1 23

Sumator (Full adder) ci ai bi si ci+1 24

Bloki funkcjonalne c.d. B. kombinacyjne B. sekwencyjne Pamięci Układy Komutacyjne MUX DMUX DEC Układy Arytmetyczne Komparator Sumator Liczniki Zliczające W górę W dół Rejestry Równoległe Przesuwające ROM 25

Q Q Q Q D D D D 1 2 3 4 1 2 3 4 CLK Rejestry Rejestry buduje się z przerzutników typu D Najprostszy rejestr: ładowanie (load) i pamiętanie 0 1 0 0 0 1 0 0 LOAD Taki rejestr nazywamy równoległo-równoległym, krótko równoległym 26

Q Q Q Q 3 1 2 4 D D D D wejście 4 1 3 2 szeregowe Rejestr przesuwający SHR 0 0 0 0 0 1 0 clk Taki rejestr nazywamy szeregowo-równoległym, krótko szeregowym 27

Q Q Q Q 3 1 2 4 wejście D D D D 4 1 3 2 szeregowe CLK Q Q Q Q D D D D 1 2 3 4 1 2 3 4 CLK Jak zbudować rejestr uniwersalny... tzn. taki, który wykonywałby funkcje zarówno rejestru równoległego , jak też szeregowego 28

...wystarczy rozbudować rejestr przesuwający Q Q Q Q 3 1 2 4 Q D wejście D D D D 4 1 3 2 Q szeregowe CLK Clock D0 D1 Sel 29

Wejścia równoległe X X X x x p 1 0 1 Wejście szeregowe R R x p s s 1 1 0 s s (Q) (Q) 2 2 Clock clock clock D D D D Wejście sterujące Y Y Y := X LOAD Y := Y HOLD Y := X LOAD Y := Y HOLD Clock D D D D Clock Y Y := SHR(xp, Y) Y := SHR(xp, Y) Q Q Q Q Wyjścia równoległe Rejestr szeregowo-równoległy Taki rejestr można rozbudowywać dalej uzyskując tzw. rejestr uniwersalny 30

Mikrooperacje rejestru LOAD HOLD SHR 0 xR 1100 1100 LOAD HOLD SHR 0010 LOAD 0110 0011 SHR – przesuwanie w prawo 0001 31

E Licznik clock Q Liczniki… …przykład syntezy licznika (zadanie 8.1 skrypt Układy logiczne w zadaniach) Zaprojektować licznik mod 8 z wejściem zezwalającym E (Enable). Przerzutniki do realizacji dobrać tak, aby uzyskać najprostszy schemat logiczny licznika. 32

Zakodowana tablica przejść licznika Zakodowana tablica przejść kod binarny Tablica przejść 33

Funkcje wzbudzeń dla przerzutników D D2 = D1 = D0 = 35

Funkcje wzbudzeń dla przerzutników T T2 = T1 = T0 = Errata do zad. 8.1 ze skryptu 36

= T E 0 = T EQ Enable Q Q Q T0 T1 T2 1 0 = = T EQ Q T Q Clock Q Q Q 2 0 1 1 1 1) Najprostszy na świecie Schemat logiczny licznika1) 37

Enable Q Q Q Q T T T T Clock Q Q Q Q Schemat ten można uogólnić… 38

Enable Q Q Q Q T T T T Clock Q Q Q Q Rst Licznik 4-bitowy 0 1 0 0 z powodzeniem może być wykorzystany do realizacji licznika uniwersalnego Wada: jest to licznik bez funkcji: LOAD (ładowanie) Realizacja funkcji ładowania dla przerzutników T jest niemożliwa Jak wybrnąć z tej sytuacji? Trzeba znać i rozumieć układy logiczne! 39

Q’ = D T Q D Q clk D = Przerzutnik T realizowany z D Równanie charakterystyczne: Q’ = f(I1,I2,Q) 40

Enable Q Q Q Q T T T T Clock Q Q Q Q Rst T Q D Q clk Licznik z wpisem równoległym.. …uzyskamy, zastępując przerzutniki T… 41

Licznik z przerzutnikami D Wprowadzając taką zmianę, jak też wprowadzając przed wejście każdego D multiplekser, uzyskujemy strukturę licznika z mikrooperacją wpisu równoległego. 42

Licznik z wpisywaniem równoległym Enable 0 Q Q D 0 1 D 0 Q 0 Q Q D 1 D 1 1 Wejścia równoległe Q Wyjścia równoległe 0 Q Q D 2 D 1 2 Q 0 Q Q D 3 D 1 3 Q Output Load carry Clock 43

X L s 1 s (Q) 2 clock Y Y := X LOAD Y := Y HOLD Y := Y+1 COUNT Licznik z wpisywaniem równoległym Enable 0 Q Q D 0 1 D 0 Q 0 Q Q D 1 D 1 1 Q 0 Q Q D 2 D 1 2 Q 0 Q Q D 3 D 1 3 Q Output Load carry Clock 44

Mikrooperacje licznika LOAD HOLD COUNT 1100 1100 LOAD HOLD COUNT 0010 LOAD 1101 1110 Zliczanie 1111 45

Pamięci typu ROM X0 n ROM N m A Xi XN-1 m Y N = 2n N słów (komórek) m-bitowych W każdym komórce pamięci zapisane jest słowo m-bitowe Pamięć ROM jest uniwersalnym układem kombinacyjnym 46

Pamięci typu ROM 0 1 2 3 4 5 6 7 Adres ROM 8 4 0 1 1 0 0 1 1 0 1 1 1 0 1 1 1 0 0 0 0 0 1 0 1 0 0 1 0 0 0 1 1 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 1 1 0 1 1 0 47