FPGA 模块代码的 开发过程

FPGA 模块代码的 开发过程. 以 FIR48 阶滤波器为例. Outline. Model Design specification Data path and controller design Test bench Synthesis and timing simulation. model. FIR 滤波器结构说明图. FIR Coefficients ( IS-2000 规范). Matlab simulation. Fix-point Coefficients and simulation. Outline. Model

FPGA 模块代码的 开发过程

E N D

Presentation Transcript

FPGA模块代码的开发过程 以FIR48阶滤波器为例

Outline • Model • Design specification • Data path and controller design • Test bench • Synthesis and timing simulation

model FIR滤波器结构说明图

Outline • Model • Design specification • Data path and controller design • Test bench • Synthesis and timing simulation

Design Specification • 1,Function 48阶fir滤波器,可同时进行I,Q两路处理 • 2,Input clk,系统时钟 reset,系统复位 data_valid,输入有效指示 din_i,I路数据输入端 din_q,Q路数据输入端

3,Output fir_i,I路数据输出端 fir_Q,Q路数据输出端 out_valid,输出有效指示 • 4,Timing 当data_valid有效时,I,Q两路同时输入缓存,然后用内部信号clk_en来选择数据通道(datapath)处理哪一路。

本程序中,对data_valid的时序有一定的要求:输入端data_valid占空比为1/N(其中N为大于一的整数,即N=2,3,4……),频率为fclk/N。只要data_valid符合上述要求,本程序都可以有效工作。本程序中,对data_valid的时序有一定的要求:输入端data_valid占空比为1/N(其中N为大于一的整数,即N=2,3,4……),频率为fclk/N。只要data_valid符合上述要求,本程序都可以有效工作。 当out_valid有效时,输出端fir_i,fir_q有效。

Outline • Model • Design specification • Data path and controller design • Test bench • Synthesis and timing simulation

Data path design • 1. 查找表模块 本部分包括6个查找表,用来保存24个系数的部分和。查找表的输入数据为din的相应位的组合。输出为对应部分和。 • 2. 部分和模块 本部分对查找表的输出进行处理,主要是符号扩展和移位相加。以查找表的输出作为自己的输入,并输出din与对应系数的乘积。

Outline • Model • Design specification • Data path and controller design • Test bench • Synthesis and timing simulation

Test bench • Test bench的测试过程如下: • 1,用matlab生成输入数据文件,并仿真生成参考输出数据文件。 • Modelsim内 • 2,读取输入数据文件,设置适当类型的变量存放这些数据。 • 3,设定模块输入信号的初值,比如:clk,reset等。 • 4,指定输入信号的变化规律,比如:clk的周期,reset何时变化等。 • 5,调用待测试模块。 • 6,当输出信号有效时,采集输出信号,并存入输出数据文件。 • 7,用其他工具(matlab,ultraedit等)将参考输出数据文件与输出数据文件进行比较。

注意: • 一,以上这些部分有些是顺序执行,有些则是并行执行,根据具体情况而定。 • 二,我们得到输出数据后,还需要将这些数据与matlab仿真结果进行逐比特对比,观察数据是否正确。 • 三,有些情况下逐比特比较结果不可行,那就要根据具体情况设计检验方法,在通信中常用的方法还有信噪比检验法。

Outline • Model • Design specification • Data path and controller design • Test bench • Synthesis and timing simulation

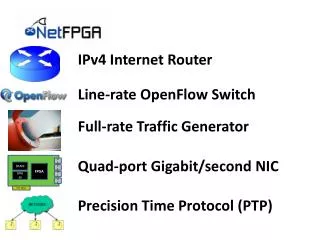

Synthesis • 我们使用相关工具进行综合(本设计使用Quartus II),我们主要关注面积和系统频率两方面。 • 面积:我们希望电路所占面积尽可能小,本设计综合后Logic Cells的数目为4681 • 系统频率:系统工作速度要尽可能快,本系统要求工作频率50MHz,但实际工作频率可达到236.57MHz(period = 4.227 ns )

Timing Simulation • 这部分是时序仿真,即在前面功能仿真基础上,加上延时信息进行仿真。 • 综合后会有两个文件生成(.vo和.sdo),我们用这两个文件以及功能仿真时所用的Testbench,进行时序仿真。 • 时序仿真和功能仿真的结果应该完全一致。