Digital System Final Project

80 likes | 325 Views

Digital System Final Project. 2010 -1 학기. 개요. 목적 : 디지털시스템 설계 경험 습득 및 설계 능력 평가 내용 : 기본 게이트를 포함한 플립플롭 , 멀티플렉서 , 디코더 , 카운터 , 3 상태 버퍼 등을 이용하여 임의의 디지털시스템 설계 방법 : max plus II 의 graphic editor, compiler, waveform editor, simulator 등을 이용하여 회로 설계 및 시뮬레이션

Digital System Final Project

E N D

Presentation Transcript

Digital SystemFinal Project 2010 -1학기

개요 • 목적: 디지털시스템 설계 경험 습득 및 설계 능력 평가 • 내용: 기본 게이트를 포함한 플립플롭, 멀티플렉서, 디코더, 카운터, 3상태 버퍼 등을 이용하여 임의의 디지털시스템 설계 • 방법: max plus II의 graphic editor, compiler, waveform editor, simulator 등을 이용하여 회로 설계 및 시뮬레이션 • 평가: 설계 item의 기능 및 완성도 report 및 발표

Example System • 예제 1. add/subtract 및 데이터 이동 기능을 갖는 간단한 CPU 기능 • 4개의 8bit register A, B, C, D • special register A는 add/subtract의 결과 저장 • 예제 2. Vending Machine • 자동판매기 제어 장치 • 예제 3. digital clock • 시, 분, 초를 나타내는 디지털 시계 • 예제 4. booth multiplier • 음수도 곱할 수 있는 곱셈기 • 그 외 교재에서 참고

설계 과정 • 팀 구성 및 주제 선정 (3인 1조) • 설계할 시스템의 선정 및 사양 정의 • 설계할 디지털 시스템의 입력/출력 정의 및 이를 이진 디지털로 표현 • 설계할 디지털 시스템의 동작 정의, state diagram 작성 • 설계한 state diagram을 반영하여 디지털 설계 tool을 활용하여 설계 진행 • 설계된 시스템과 동일한 기능을 가지는 회로를 가능한 작은 비용 (logic components)를 가지도록 최적화 • 다양한 입력 값에 대한 출력 확인을 통한 동작 확인 • 최종 발표 및 설계 보고서 제출

시스템 요구사항 분석서 • 팀 구성원( 이름, 학번, 연락처 ) 홍길동, 0434233, 010-2342-xxxx(예) • 과제 목표8-bit 곱셈기 구현 • 요구 사항(예) 1. 각 레지스터는 clock에 동기화됨. 2. 모든 레지스터는 플립플롭을 이용하여 직접 구현해야 함. 3. 외부 입력으로 부터 레지스터에 적재 가능. 4. 8 비트 레지스터 A(피젯수)와 B(젯수) 는 곱할 두 수를 가지고 있음 5. 16 비트 결과는 AB 레지스터에 저장된다. 6. 8 clock 기간 동안 곱셈을 마침 • 분석 내용 각 요구 사항에 대해 어떻게 할 것인가? 에 대해 작성할 것.

시스템 설계 사양서 • 팀 구성원( 이름, 학번, 연락처 ) 홍길동, 0434233, 010-2342-xxxx(예) • 과제 목표 8bit multiplier를 구현 • 기능(예) - 입력 8bit을 A와 B에 적재하는 기능. - 레지스터 B의 내용을 한 비트 씩 shift 하면서 1이면 피제수(A)를 더하고 0이면 더하지 않는다. 결과 물이 AB 연결된 16비트 레지스터에 저장된다. - 8bit adder를 구현. • 입출력 변수(예) 1. input : IN[8-bit], CLK[1-bit], RESET[1-bit] , LOAD[1 bit], 2. output : OUT[16-bit]

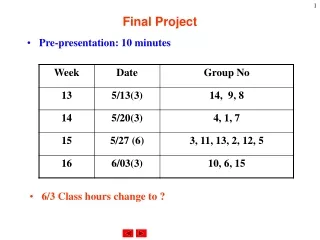

보고서 제출 및 발표 • 요구사항 분석서 제출: 5월 25일 화요일 • 최종 보고서 제출: 6월 8일 화요일 • 최종 보고서 양식 • 팀원의 각 참여도(%) • 시스템 설계 사양서 • 회로도 • 시뮬레이션 결과물 • 발표: 10분/조

평가 1) 문제 정의, 설계 수행 방법 및 Team work (30%) - 설계할 디지털 시스템의 선정(참신성과 적절한 복잡도) - 팀원간의 협동 (팀원의 역할 명시 및 각 팀원이 전체 과제에 대한 이해도) • 시스템의 명세, state diagram, 다양한 입력에 따른 시험 결과 2) 설계 성취도 (40%) - 명세에 제시된 바와 일치하는 동작 확보 (다양한 입력에 대한 검증) • 동일 기능의 설계로부터 최적화한 정도 및 방법 3) 발표력 (30%) - 결과발표 (요구사항 및 설계 과정)를 통해 평가