Evolution of CPS Readout Architectures Achieved by Christine Hu-Guo

160 likes | 190 Views

Learn about the technological advancements in CPS readout architectures, including image vs. hits, chromatic vs. monochromatic designs, and the evolution from 1st to 3rd generation architectures. Explore the impacts on sensor architecture and design strategies.

Evolution of CPS Readout Architectures Achieved by Christine Hu-Guo

E N D

Presentation Transcript

Overall sensor architecture designs achievedChristine Hu-Guo (on behalf of the PICSEL team of IPHC-Strasbourg)

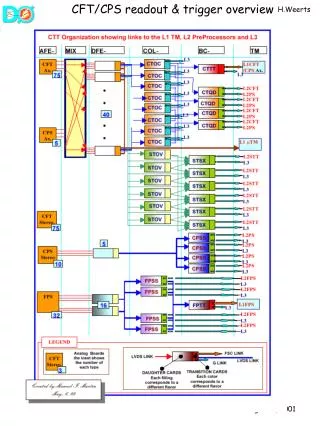

CPS Readout Architectures Images Hits Chromatic Mono-chromatic The choice of CPS readout architecture depends on its applications Images vs Hits: • Images: need to read all pixels rolling shutter readout limited by RO speed • Hits: send only information of the hit pixels sparse RO high speed Chromatic vs Monochromatic: • Chromatic: analogue output or n-bit ADC power consume + time • Monochromatic: binary output IPHC christine.hu@in2p3.fr

CPS Architecture’s Evolution 1st generation of CPS 2nd generation of CPS 3rd generation of CPS Twin well processes: 0.6-0.35 µm Quadruple well process: 0.18 µm Twin well 0.6-0.35 µm process: only NMOS in pixel array is allowed. N-well used to host PMOS would compete for charge collection with the sensing N-well diode limits choice of readout architecture strategy • 1st generation: 2/3 T pixels, rolling shutter readout with analogue output • MIMOSA5 (~3.4 cm²), MimoSTAR (~2 cm²) first demonstrators • 2nd generation: in-pixel amp & CDS using only NMOS, AD conversion and zero suppression at periphery • MIMOSA26 (2.9 cm²): EUDET telescope, MIMOSA28 (4.6 cm²): STAR PXL excellent performances! Quadruple well 0.18 µm process: both N & P MOS can be used. N-well for PMOS is shielded by Deep P-well Widens choice of readout architecture strategies • 3rd generation: in-pixel amp+shaper, in-pixel ADC, … data driven readout power saving + speed! • ALPIDE (4.5 cm²): ALICE-ITS, MIMOSIS (~5 cm², design in progress): CBM-MVD Contribution to process and detector concept validation & In-pixel electronics in ITS collaboration IPHC christine.hu@in2p3.fr

Technology dependent constant MOS transistor width and length Gate oxide capacitance per unit area Transistor transconductance Boltzmann constant Absolute temperature Weak inversion slope Often around ½ - 2/3 in strong inversion Figure of Merit S/N vs Design Optimisation ~ ~ Flicker noise (1/f) Thermal noise Signal: • Small collection electrode, small input transistor, short inter connection for low C • BUT too small diode does not favour the charge collection Noise: • Sensing Diode: • Shot noise due to leakage current, especially after irradiation • Ileak is proportional to diode dimensions • Shot noise is proportional to integration time, negligible for short integration time O(1 µs) • RTS (Random Telegraph Signal) noise • Input Transistor: in Weak inversion:Strong inversion: • To minimise • Flicker noise: large input transistor large Ctin & area • Thermal noise Large gm , high power • Both of two noise: Use a filter (band-pass) 1. trade-off between Noise & Power 2. trade-off between MOS in very weak inversion & dispersion 3. need a filter IPHC christine.hu@in2p3.fr

Figure of Merit S/N vs Design Optimisation (2) IPHC christine.hu@in2p3.fr • In-pixel transistors RTS noise: increases as the feature size of the devices is scaled down • Impact on dimensions (W and L) of the in-pixel transistors • PMOS has better performance than NMOS • Negligible if integration time small enough • Reset noise: • Contributions from: • Other transistors in pre-amplifier stage is not negligible • Next stages • High gain in the first stage (G1) tends to mitigate the total noise Maximise the figure of merit is the design guideline

A Typical Readout Chain AMP: Iow noise pre-amplifier Filter: filter ADC: Analogue to digital conversion (1 bit: discriminator) It may be implemented in-pixel level or at column level underneath the pixel array Data compression: Only hit pixels information is sent It is at chip edge level underneath the pixel array OR implemented in-column level inside pixel array Data transmission: x Gbit/s link at chip edge level SoC (System on Chip): Steering, slow control, bais DAC, … Readout mode: 2nd CPS generation: Rolling Shutter readout architecture = best trade-off between performance, design complexity, pixel dimension, power, … in a twin-well process 3rd CPS generation: Sparse readout depends on applications IPHC christine.hu@in2p3.fr

2nd CPS Generation Only NMOS transistors CDS Preamplifier N_Well Diode Output Buffer Design based on the rolling shutter readout architecture, addresses 3 issues: • Increasing S/N at pixel-level in-pixel Preamplifier + CDS • A to D Conversion: at the end of column level (twin well) • Zero suppression (SUZE) at chip edge level Power vs speed: • Power:only the selected row (N=1) to be read is PWR ON • Speed:N rows pixels are read out in // • Integration time = frame readout time Sensing diode: Andrei talk Preamplifier: • It is only active when the row is selected to be read • Readout speed (200 ns/row) short time from start to steady • Requires current to drive increase power consumption • Large bandwidth noise • Short start-up time leads to a moderate gain • Typical gain value: < 5 Filter = cDS achieved by a clamping technique • CDS acts as a high pass filter It can provide suppression of low freq. noise Pixel output: SF needed to drive analogue signal for a few cm column line power consume! IPHC christine.hu@in2p3.fr

2nd CPS Generation (2) Column-level 1-bit ADC (discriminator) • Because 1, pre-amplifier gain not high enough 2, pixel to pixel fixed pattern noise Discriminators need to use an offset compensation technique • Both OOS (Out Offset Storage) and IOS (Input Offset Storage) are employed • Layout with restricted width = pixel pitch (~20 µm) SUZE finds groups of hit pixels and sends their addresses and corresponding encoded pattern • The purpose is to skip non hit pixels in order to obtain a data compression factor ranging from 10 to 1000 • Up to 4 contiguous pixels encoded in 2 bits, only the address of the 1st pixel is sent • Simple logic & full digital design to be implemented • Processing capability: 0.5x106 hits /cm²/s Steering, slow control (JTAG), bias DAC, temperature sensor, regulator for the clamping voltage, LVDS Tx/Rx, … are implemented at chip edge SoC! IPHC christine.hu@in2p3.fr

3rd CPS Generation 2nd generation 3rd generation More functionalities may be integrated inside a pixel thanks to quadruple well process Example of MIMOSIS: CBM (Compact Baryonic Matter, experiment at FAIR) MVD (Micro Vertex Detector) Some requirements related to the sensor’s architecture • Fast read-out: <~10 µs • Excellent spatial resolution: ~5 µm • Robustness to radiation environment: ~10 higher than ALPIDE • TID: 3 Mrad @ -20 °C & 1 Mrad @ + 30 °C • NIEL: 3 x 1013 neq/cm² @ -20 °C & 1 x 1013 neq/cm² @ +30 °C • Power consumption: • Station 0&1: <300 mW/cm², Station 2&3: <200 mW/cm² • Hit rate capability (most exposed 4x4 mm²) • Average: ~1.5 x 105/mm²/s • Peak: ~7 x 105/mm²/s, O(100) higher than ALPIDE • Big fluctuation of beam Elastic buffer to store >= 5 consecutive frames with maximum hit rate IPHC christine.hu@in2p3.fr Beam Profile over Time 10 µs binning, y-scale in arbitrary units

MIMOSIS Sensor Architecture of the Pixel array is pursued based on ALPIDE chip We have to improve: 1. the radiation tolerance capability 2. the ability to handle the higher event rate Design based on the data driven readout architecture, addresses 4 issues: • Improving S/N at pixel-level: • Low power consumption (O(10) nW) Each pixel features a continuously power active • High gain (~100) amplifier with shaping (~µs) • A to D Conversion at pixel-level: • Very simple 1-bit ADC thanks to high amplifier gain • Analogue buffer driving the long distance column line is no longer needed power-saving • Data driven readout at column-level & inside pixel array • only zero-suppressed data are transferred speedy • Chip readout unit, Elastic buffer, Slow control, Bias DAC, PLL, … all at chip edge level • Totally new design!!! IPHC christine.hu@in2p3.fr

Pixel Array Matrix (504 x 1024) Pixel dimensions: 30.24 x 26.88 µm² x16 Region 1 Reg. 2 Reg. 3 Reg.4 x8 504 pixels 504 pixels Pixel Pixel Priority Encoder Pixel Pixel Pixel Pixel Pixel Pixel Pixel Pixel Pixel Pixel Dig Dig Analog FE Analog FE Bias Pixel configuration 10 bits @ 20 MHz IPHC christine.hu@in2p3.fr Every pixel contains: a sensing element, a preamplifier/shaper, a discriminator, 2 digital buffers & a part of data driven readout encoder Priority encoder: 1 encoder per double column (2x504 pixels) • 504 rows chosen to allow including header & frame counter inside data within 16 bit words 1 region has 8 double columns, 64 regions are running in parallel • Increasing the ability to handle the higher event rate. The number of regions depends on the values of the peak hit rate, the probability and the Priority Encoder readout speed 8 Priority Encoders in a region are read-out in serial @ 20 MHz Readout frame per frame in 5 µs pipeline mode

In-Pixel Front End Circuit IMO=20 nA IM4=500 pA VIN=Qin/Cin Vout_A Threshold I=IMO+IM4 One of options: ALPIDE front end circuit • Combine three functionalities: • Amplifier + Shaper + Discriminator • Charge transfer from a large C to a small C to generate V gain AC coupled version: compare to DC coupled version foreseen to evaluate TID performance Other solutions: need to be tested IPHC christine.hu@in2p3.fr

In-Pixel Logic & Memory Buffers 26.88 µm • The block dimensions: 13.5x13.8 µm² • 75 transistors in total • Guarding ring ~20% surface • Density: ~ 0.5 transistors/µm² 30.24 µm Full custom complex gate design to minimise the surface • Optimising the dimension, element placements, signal path and modelisation Pixel logic implementation constraints: • Space limited by sensing node and pixel dimensions • Integration to digital flow verification Timing model generation and verification • Extraction of Verilog description & timing model using Liberate tool • Validate timing model by comparing with analog simulation IPHC christine.hu@in2p3.fr

Column-Level Data Driven Readout Data driven readout is based on an arbiter tree scheme with hierarchical address encoders and reset decoders An example of a single bit 4 to 2 encoder Basic logic contains three units: • Fast OR VALID • Address Encoder • Reset Decoder Repeated tree structure + buffering Using full digital design flow Functionality vs. pixel pitch IPHC christine.hu@in2p3.fr

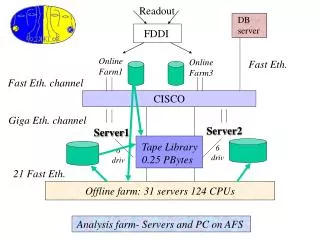

Periphery Circuitry • Steering the Priority Encoder of the Matrix & Finding Clusters of Pixels • Read out a “Region” of 8 double columns of pixels, the 64 regions of the matrix operate in parallel • Find and encode clusters of a maximum of 4 contiguous pixels in a 3-bit word • Tag the encoded pixel with 13 address bits • Gathering the data of the 64 PEDCF: • Introduce the Region address as a header • Pack the successive data through 2 successive levels respectively into 64 and 16 memory buffers • Finalizing data collection • Add Frame information (frame header, trailer) • Remove unoccupied space between 2 data streams • Handling the data • Manage the random data flow due to beam fluctuation in order to obtain a sustainable output data rate • Implement an elastic buffer & decrease the flow from 20 Gbit/s max to 320 Mbit/s per output • Handle up to 8 serial outputs Used methodology • Development performed block by block without partitioning & time budgeting • Assembly under encounter • STA via Tempus Bias DAC, PLL, SLVSTX/RX: analogue & mixed design MIMOSIS Data Flow Processing has to gather, compress & classify the collected data issued from the matrix. It is performed on long distances (3 cm) and large data buses, these constraints require successive memory buffers: IPHC christine.hu@in2p3.fr

Summary & Conclusions Choice of CPS readout architecture depends on its applications 3 CPS generations have been developed in different CMOS technologies CPS design is always a tradeoff between: pixel pith, power consumption, readout speed We are open for any promising technology in order to improve the performance CPS IPHC christine.hu@in2p3.fr