Network On Chip Cache Coherency

Network On Chip Cache Coherency. Final report, part B Students: Zemer Tzach Kalifon Ethan Instructor: Walter Isaschar Winter 2009. Agenda. General concepts. Description of the coherency protocol. Architecture design. Components implementation. Simulations.

Network On Chip Cache Coherency

E N D

Presentation Transcript

Network On Chip Cache Coherency Final report, part B Students:ZemerTzach Kalifon Ethan Instructor: Walter Isaschar Winter 2009

Agenda • General concepts. • Description of the coherency protocol. • Architecture design. • Components implementation. • Simulations. • Functionality demonstration . Network On Chip - Cache Coherency

General Concepts Network On Chip - Cache Coherency

General Background • Modern CPU’s are based on CMP – Chip-Multi Processor. • Improved performance is achieved by “Distribution and Parallelism”. • Cores interact by using NoC – Network on Chip. Network On Chip - Cache Coherency

NoC General Diagram Network On Chip - Cache Coherency 5

NoC Characteristics Wormhole packet routing. Packet’s path is X-Y. Units can communicate simultaneously. Reduce power consumption. Scalability. Network On Chip - Cache Coherency 6

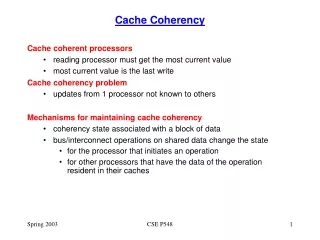

Cache Coherency Cache: On chip fast temporary storage. Cache Coherency: CMP cores use only up to date data. Traditionally, Cache Coherency achieved by central memory control unit. Network On Chip - Cache Coherency 7

Traditionally Cache Coherency Network On Chip - Cache Coherency 8

Problem Description • Prior Cache Coherency protocols are irrelevant – NoC doesn’t have central unit. • Adding such unit will damage both NoC’s scalability and parallelism. Network On Chip - Cache Coherency

Solution Requirements • High performance: • Avoid “Hot Spots” and “Bottlenecks”. • Minimize resources. • Won’t affect main NoC characteristics (e.g. scalability). Network On Chip - Cache Coherency

Solution Basics • Memory control distribution according to memory spaces. • Placement of control units as part of the NoC. Network On Chip - Cache Coherency

Solution Diagram Network On Chip - Cache Coherency

Solution General Example • CPU refer to the appropriate Controller. • Controller order transfer of data. • Other CPU sends the cache line. • Read Miss on line 1000. Network On Chip - Cache Coherency

Project Goal • Design and implement Cache Coherency protocol for CMP based NoC. • Implement NoC (part one). • Implement Cache Coherency support for NoC (part two). Network On Chip - Cache Coherency

Coherency Protocol Network On Chip - Cache Coherency

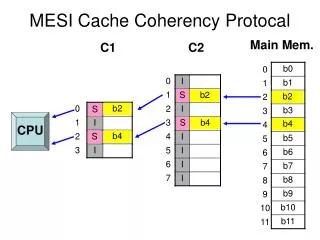

General Description • Three types of transactions: Read, Read for Ownership and Invalidation. • Cache line’s status can be I/S/E (Invalid/Shared/Exclusive respectively). • Each cache control unit keeps journal which determines line’s status. • Requests are first addressed to the appropriate cache control unit. Network On Chip - Cache Coherency

Protocol’s Terminology • Requester. • Home Node. • Closest Sharer. • Owner. Network On Chip - Cache Coherency

Read Miss: Line is Shared Network On Chip - Cache Coherency

Write Miss: Line is Shared Network On Chip - Cache Coherency

Design difficulties (1st example) Network On Chip - Cache Coherency

Design difficulties (2nd example) Network On Chip - Cache Coherency

Protocol’s Features • Parallel handling of Read requests. • Data is forwarded by the Closest Sharer. • Transparency: any CPU which uses M/E/S/I is supported. • The protocol supports strongly consistent processors. Network On Chip - Cache Coherency

Architecture Network On Chip - Cache Coherency

CMP Diagram Network On Chip - Cache Coherency

CPU Node Structure Network On Chip - Cache Coherency

NoC Interface • Functions as a gateway to the NoC. • Packing/unpacking flits into/from NoC’s Packets. • Transmit and receive data simultaneously. Network On Chip - Cache Coherency

NoC Interface Structure Network On Chip - Cache Coherency

CPU Interface • Adapting between NoC’s Cache Coherency Protocol and the CPU. • Translating NoC’s Packets into/from FSB transactions. • CPU transactions doesn’t prevent the CPU Interface from handling the Protocol’s packets. Network On Chip - Cache Coherency

CPU Interface Structure Network On Chip - Cache Coherency

Controller Node Structure Network On Chip - Cache Coherency

Cache Coherency Controller • Manages the Coherency Protocol. • Each CCC (Cache Coherency Controller) is responsible for a specific set of the Memory Lines. • The Directory Table (DT) holds the status of the above Lines as well as several protocol’s information bits. Network On Chip - Cache Coherency

CCC Structure Network On Chip - Cache Coherency

DT General Structure • The DT will contain the following data for each Line: Network On Chip - Cache Coherency

Architecture Features • Message’s length vary according to its purpose. Reduces NoC’s congestion. • Messages carry the transaction information (reduces HW requirements). • Transaction can be blocked by memory update only (allows high parallelism). • Scalable. Network On Chip - Cache Coherency

CMPImplementation Network On Chip - Cache Coherency

CMP Characteristics • Size of memory unit is 1 [Byte]. • Cache line comprise 2 memory units (can be enlarged). • Size of memory is 16 [Byte]. • CPU’s actions are determined by the user. Network On Chip - Cache Coherency

CPU Implementation Network On Chip - Cache Coherency

CPU Node Implementation Network On Chip - Cache Coherency

CCC Node Implementation Network On Chip - Cache Coherency

CMP Implementation Network On Chip - Cache Coherency

Synthesis Parameters Network On Chip - Cache Coherency

System Performance • System’s clock frequency is 100 [MHz]. • CPU’s hold-up (in cycles): Network On Chip - Cache Coherency

System Performance • M – Memory penalty. • C – Dependant on number of CPUs. • Delay in all nodes is one/two cycle. • In larger systems network factor becomes greater. Network On Chip - Cache Coherency

CMPSimulations Network On Chip - Cache Coherency

Read Miss: Line is Shared (1) • CPU1x1 reads cache line. The appropriate line is stored in CPU0x0. 2 1 Network On Chip - Cache Coherency

Read Miss: Line is Shared (2) 2 3 4 1 Network On Chip - Cache Coherency

Read Miss: Line is Shared (3) 2 6 1 5 Network On Chip - Cache Coherency

Read Miss: Line is Exclusive (1) • CPU1x1 reads for ownership. The appropriate line is stored in CPU0x0. 2 2 1 1 Network On Chip - Cache Coherency

Read Miss: Line is Exclusive (2) 2 3 1 4 Network On Chip - Cache Coherency

Read Miss: Line is Exclusive (3) 2 5 1 Network On Chip - Cache Coherency