Characterization of Cache Coherency in Network-on-Chip Architectures for Multi-Core CPUs

This presentation details the characterization of cache coherency in Network-on-Chip (NoC) architectures within multi-core CPUs. It discusses the challenges of maintaining cache coherency when utilizing NoC, particularly how the complexity increases and traffic throughput is affected. The project involves designing a cache coherency protocol and implementing a router for NoC, utilizing Xilinx VirtexII Pro FPGA. Goals include assembling a CMP based on NoC and ensuring consistent access to data across cores, ultimately enhancing performance through distribution and parallelism.

Characterization of Cache Coherency in Network-on-Chip Architectures for Multi-Core CPUs

E N D

Presentation Transcript

Network On Chip Cache Coherency Characterization presentation Students: Zemer Tzach Kalifon Ethan Instructor: Walter Isaschar Spring 2008

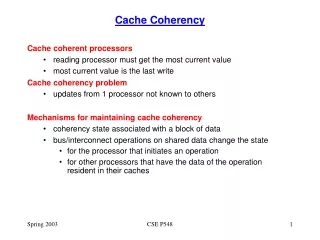

General Background • Modern CPU’s are based on CMP - Multi-Core CPU. • Improved performance is achieved by “Distribution and Parallelism”. • Cores interact by using NoC – Network on Chip. Network On Chip - Cache Coherency

General Background Network On Chip - Cache Coherency 3

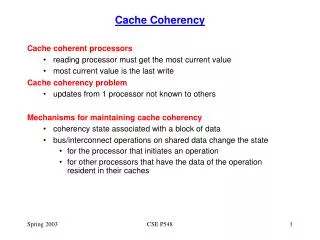

General Background Cache Coherency: CMP cores use only consistent data. Originally, Cache Coherency in CMP was achieved by using a central memory control unit. Network On Chip - Cache Coherency 4

General Background Network On Chip - Cache Coherency 5

Problem Description • When using NoC, Cache Coherency managing becomes more complicated. • When using NoC, Cache Coherency managing protocol increases NoC’s traffic. Network On Chip - Cache Coherency

Problem Description Network On Chip - Cache Coherency 7

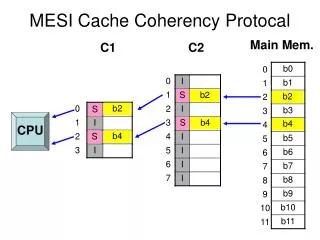

Solution • Memory control distribution among a number of units according to memory spaces. • Placement of control units next to the network’s cores. Network On Chip - Cache Coherency

Solution Description Network On Chip - Cache Coherency

Project’s Goals • Primary Goal: Design and implement Cache Coherency protocol for CMP. • Implement router for NoC. • Assemble CMP based on NoC. Network On Chip - Cache Coherency

Environment • Xilinx VirtexII Pro FPGA. • Design Tools: HDL Designer, EDK 9.2i, Chipscope 9.2i, ISE 9.2i. Network On Chip - Cache Coherency

Project Schedule (1st Semester) • Familiarize with design tools – 3 weeks. • Familiarize with VirtexII Pro FPGA (application & components) – 4 weeks. • Design & Implement NoC’s router – 5 weeks. Network On Chip - Cache Coherency

Project Schedule (2nd Semester) • Assemble CMP using our router implementation. • Design Cache Coherency protocol for CMP based on faculty research. • Implement the protocol as part of the assembled CMP. Network On Chip - Cache Coherency