CBM

Status of the Development of Electronics Research in the Calcutta University towards CBM Objective Dr. Amlan Chakrabarti Dr. Sanatan Chattopadhyay Dr. Sudipta Bandopahyaya Mr. Suman Sau Mr. Mridul Sengupta. CBM. 1. Outline. Introduction Commitment Progress

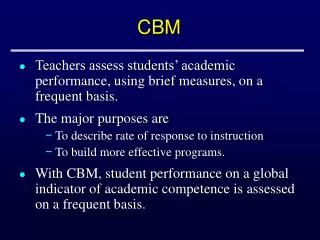

CBM

E N D

Presentation Transcript

Status of the Development of Electronics Research in the Calcutta University towards CBM Objective Dr. Amlan Chakrabarti Dr. Sanatan Chattopadhyay Dr. Sudipta Bandopahyaya Mr. Suman Sau Mr. Mridul Sengupta CBM 1

Outline • Introduction • Commitment • Progress - Purchase and Recruitment of Fellows - Technical • Future Plan CBM 2

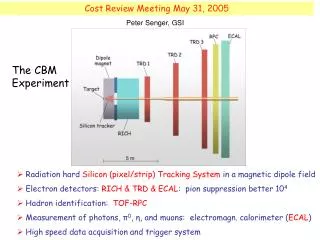

Introduction • Calcutta University participated in the project for developing electronic circuits, especially, for developing high speed read-out for data communication. • In this context, it was also aimed to develop a design and characterization laboratory. • To this direction, the FPGA based Kits have been purchased and installed. These are now running without hazards. • Some of the test results are ready to report. CBM 3

Commitment • Development / Building of a Laboratory / Centre. • Purchasing relevant Software / Tools / Kits. • Installing and Testing the Software / Tools / Kits. CBM 4

Purchase and Recruitment of Fellows • FPGA Kits Purchased • Spartan 3E Starter Kit • Virtex 4 LX/SX Development Board • P160 Analog Module • Software Purchase • Xilinx ISE 11.1 System Edition • Quotation for Synopsis has been received • Recruitment of Fellows • Two research fellows have been recruited for this purpose CBM 5

Technical Activities • Interfacing the PS/2 Keyboard with FPGA • Data ( Image data) Transfer (FPGA to VGA) • Accessing SRAM(IS61LV25616AL) • Transmitting data through serial port (FPGA to Computer through RS232 serial port) CBM 6

CBM Technical 1 • Plan (Schematic) VGA DB 15 Connector RS232 FPGA Spartan 3E Downloading Interfacing with PS/2 Keyboard Bit File MATLAB Data (Image) .coe file Ethernet (10/100) .bmp file

CBM Technical 2 • Interfacing to the PS/2 Keyboard Interfacing with PS/2 Keyboard Keyboard_clk Scan_Code[7..0] Keboard_Data Scan_ready Clock Spartan-3E Reset Read Led [7..0] • Identification of Scan Codes of Key board through LED of FPGA (Spartan 3/Spartan 3E)

CBM Technical 3 • Data ( Image data)Transfer (FPGA to VGA) Clock Red VGA Sync Green SPARTAN 3E Blue Pixel row Pixel coloum VGA_Red VGA_Green VGA_Blue HS VS Pixel Clock Address O/P BROM Row Address Coloum Address MATLAB .bmp file .coe file IP Core : Block Memory Generator v3.1 • Data Transfer from FPGA(Spartan-3E) to VGA • Image raw data(.COE File) are stored externally in ROM

CBM Decoder Ad[0..17] 256k-by-16 Cell array dio(upper) dio(lower) ce_n we_n Control Circuit oe_n lb_n ub_n Technical 4 • Accessing SRAM(IS61LV25616AL) • Write data into SRAM (Input from dip switch) • Read data from SRAM and show it in LED of the board • Control block signals are controls the Read/Write operation in SRAM

CBM Technical 5 • Transmitted data (FPGA to Computer through RS232 serial port) Download bit file through Platform Cable USB II Running EDK11.1 in PC USB Hyper Terminal • Bit files are downloaded to FPGA using Xilinx Platform Cable USB II • FPGA board is connected to PC through the RS232 port using RS232 Cable Spartan 3/3E FPGA Microblaze RS232 port RS232 cable IP Core : RS232_UART_Lite

Analog module interfacing with FPGA Virtex-4LX/SX Development Board P160 Analog Module CBM 12

Analog module interfacing with FPGA A1 A2 B1 B2 DDR Memory High Speed Ethernet A39 A40 B39 B40 Virtex-4LX/SX Development Board JX2 JX1 CBM 13

Laboratory Snapshots (1) Downloading Bit File into FPGA Spartan-3 KIT CBM 14

Laboratory Snapshots (2) Spartan-3 KIT(Bottom Left) AND Spartan -3E KIT(Top Right) CBM 15

Laboratory Snapshots (3) Output of Transmitted data (picture of a sample code on- (FPGA to Computer through -execution ) RS232 serial port) CBM 16

Laboratory Snapshots (4) • Set ups in the Laboratory Various pictures of interfacing the PS/2 Keyboard CBM 17

Laboratory Snapshots (5) • Set ups in the Laboratory Various pictures of interfacing the VGA Monitor VGA DISPLAY CBM 18

Future Plan • Development of Ethernet(10/100) protocol for data Communication in Spartan 3E and Virtex-5. • Interfacing P160 Analog Module with Xilinx Virtex-4 LX/SX Development Kit and sending the captured Data through its Ethernet Port. CBM 19