Hardware Implementation Issues on Viterbi Decoder

Hardware Implementation Issues on Viterbi Decoder. Speaker : Meng-Hau Wu Advisor : Tzi-Dar Chiueh Date : May 31, 2004. Outline. Review of Viterbi algorithm Hardware implementation issues Branch Metric Computation (BMC) Add-Compare-Select (ACS)

Hardware Implementation Issues on Viterbi Decoder

E N D

Presentation Transcript

Hardware Implementation Issues on Viterbi Decoder Speaker : Meng-Hau Wu Advisor : Tzi-Dar Chiueh Date : May 31, 2004

Outline • Review of Viterbi algorithm • Hardware implementation issues • Branch Metric Computation (BMC) • Add-Compare-Select (ACS) • Survivor Memory Management (SMM) • Conclusion • Reference

Encoding Process • Take convolutional code as an example n=2 k=1 m=2

Decoding Process • Maximum Likelihood Sequence Estimator (MLSE) (Euclidian distance, Hamming distance)

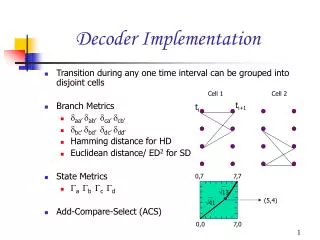

Viterbi Algorithm • There are only 2mk paths will survive • All survivor paths will merge at the same state about 5m stages ago

Hardware implementation issues -Branch Metric Computation (BMC) -Add-Compare-Select (ACS) -Survivor Memory Management (SMM)

Hard-Decision • Branch metric is irrelative to modulation and architecture used • Use Hamming distance as branch metric

Soft-Decision (1/3) • Branch metric depends on modulation and architecture

Comparison • Hard decision • Branch metric is irrelative to modulation and architecture used • Use Hamming distance as branch metric • Soft decision • Branch metric depends on modulation and architecture • By definition

Hardware implementation issues -Branch Metric Computation (BMC) -Add-Compare-Select (ACS) -Survivor Memory Management (SMM)

Basic Concept Overflow problem!!

Overflow Prevention • Modulo normalization • The output of Viterbi decoder only depends on difference of metrics • The difference between metrics is bounded • Two’s complement arithmetic [2]

q1 s s1 q2 s2 0 t-n t Bounded Difference Between Metrics [2]

Given |m1-m2|<C/2, then m1<m2 if and only if Modulo normalization (1/2) Concept : • Modular arithmetic • mj = (mj+C/2)(mod C)-C/2 • We allow overflow and transform PM from one domain (straight line) to another domain (circle), such that we can use finite-length register [3] =>This keeps the relative relationship between m1 and m2, though loses the absolute information of them

Modulo normalization (1/2) Implementation : We use “2’s complement arithmetic” to replace unsigned arithmetic and comparison => Given |m1-m2|<C/2, then m1<m2 if and only if m1-m2<0 (in 2’s complement sense) [3] 0001 (1) -) 1111 (-1) 0010 (2) 1001 (-7) -) 0111 (7) 0010 (2) -1 0 1 -7 0 7

Other Overflow Prevention Methods • Reset • Variable shift • Fixed shift [3]

Hardware implementation issues -Branch Metric Computation (BMC) -Add-Compare-Select (ACS) -Survivor Memory Management (SMM)

Trace-back Algorithm (1/3) • K-pointer even [4] 2k memory block

Trace-back Algorithm (2/3) • K-pointer odd [4] 2k-1 memory block

Trace-back Algorithm (3/3) • One-pointer [4] s+1 memory block

Comparison (1/2) • Exchange register • Simple (advantage) • Large interconnection area (disadvantage) • Trace-back • Smaller area when storage element are many • More complicated • Large RAM access power

Comparison (2/2) • K-pointer • Harmonic clock rate • Larger area • One-pointer • Smaller area • Different clock rate

Conclusion • Viterbi decoder can be divided into three parts • Branch Metric Computation (BMC) • Hard decision • Soft decision • Add-Compare-Select (ACS) • Modulo normalized • Survivor Memory Management (SMM) • Register exchange • Trace back • K-pointer even • K-pointer odd • One-pointer

Reference • [1] Modified Viterbi Algorithm and 802.11a Codec DesignTe-Wei Chang, MS thesis, 2002 • [2] An alternative to metric rescaling in Viterbi decodersHekstra, A.P.;Communications, IEEE Transactions on , Volume: 37 , Issue: 11 , Nov. 1989 Pages:1220 – 1222 • [3] VLSI architectures for metric normalization in the Viterbi algorithmShung, C.B.; Siegel, P.H.; Ungerboeck, G.; Thapar, H.K.;Communications, 1990. ICC 90, Including Supercomm Technical Sessions. SUPERCOMM/ICC '90. Conference Record., IEEE International Conference on , 16-19 April 1990 Pages:1723 - 1728 vol.4 • [4] FPGA Realization of the Viterbi Decoder for HDSL2 SystemsFeng Lo, MS thesis, 2000