L2 Status

This report provides an overview of the current status and progress of the L2 commissioning efforts as of September 14, 2001. Key topics include collaboration among institutions such as MSU, Fermilab, and others, along with updates on infrastructure readiness, power requirements, and safety clearance processes. Specific advancements in firmware, hardware assembly, and testing of critical components are detailed. Additionally, it highlights ongoing issues, upcoming tasks, and the successful integration of various technologies required for efficient operation.

L2 Status

E N D

Presentation Transcript

L2 Status James T. Linnemann MSU Collaboration Meeting September 14, 2001

Who? • Now commissioning: • Arizona, Columbia, Maryland, Michigan/CDF • MSU, Munich, Nebraska, NIU, Oklahoma • Saclay, Stony Brook, UIC, Virginia • Fermilab ESE (Green, Kwarciany, Zmuda) • Coming Soon • BU, Florida State, Orsay • A lot of good, hardworking people are responsible for L2 progress.

Infrastructure • Power, cooling, cabling all in place except • Intra-crate cables • Last run of muon cables being re-cut • Safety clearance for power in process • All cards needed built and on site except • last 11 alphas being assembled this week

FIC: G-link receiver(all crates but muon) • FPGA code being tweaked • Some vme problems remain • commissioning modes only; progress being made • Extra data word in G-link? • Fix being tested • FPGA compiler problems probably resolved • Distraction: “test” version used nonexistent resources • Fermilab/ESE support for commissioning • Met this week with Saclay experts

MBTworkhorse I/O card • 31 cards in hand (24 work; 16 at Fermi) • 4 need diagnosis/repair; 3 dead; 11+6 needed • Before install: stable SCL firmware • Estimate: September/October installation • firmware all written; being debugged (good turnaround) • Scl_init sequence; L1, L2 busy (easier) • Multi-card broadcast: need testing at FNAL • 128 bit fanout needs testing at FNAL with Edmunds: Oct • Some marginal timing being chased • Results write to Global: needs to be re-integrated • May need to tweak output amplitude • Monitoring functions: need to test at FNAL

Alpha • First Production: • 4-6 fully work (7 max); 2 back soon; break/fix about 1/week • Most: multiple vias fixed and a BGA replaced • 17+2 abandoned • Broken CIA BGA not replaceable (center of board; vias too fragile) • PIO to Alpha not working (firmware)early October • concentrate on 1 Alpha/crate • Second Production: • Pre-production boards work • DMA fixes incorporated in layout • Learned can successfully replace CIA BGA (better than unreliable socket!) • new supplier for raw boards, better assembly (failures diagnosed; site visits) • 11 more being built now: earliest end September • Need 15 for nominal system (+7 for test stand)

Betareplacement processor • Intel Compact PCI card • 2-3 Alpha in CPU • First card received and being tested • Hold in 9u card with custom devices (3 BGA’s) • Universe Chip VME interface • commercial 64-bit PCI interface chip • Mbus and other logic in FPGA • Good start on low-level software • Prep for PCI device drivers • Schedule: (quote soon) • Schematic done; starting layout • Firmware specs written; starting Verilog coding soon • Prototypes available for testing December • Production: early summer

CIC and SFO • CIC (L2Muinput card) installed; inputs cabled • SFO (fanout): all but 2 at Fermi • Needed by Muon system, and test stand • Very useful for commissioning • May have other uses during running • All cards work in most important modes • For one mode, have to hand-select cards • Only need 2 working in 1:12 fanout mode • Investigating why only half do, but half of 25 is plenty

SLIC • Basic Operating System done • First algorithm tests (Mu Central) OK • Meet speed and efficiency requirements • Other algorithms ready for download • tested in emulator • Implementing monitoring scheme

Miscellaneous Interface Hardware • 16 to 128 bit mux add-on to MBT (UMd) • Returns L2 trigger mask to L2HWFW Sep/Oct • L1HWFW to L2 Global (via FIC) (MSU) • Optical Split: L1 trigger mask Aug/Oct • dummy content: fixed + event ID • Monitoring of Alphas by L1 Scalers (MSU) • Passive cable formatting card Oct

CommissioningAt Last • L1SCL-MBT-Alpha-VBD-L3 milestone met • One channel “data”, real frame software, in MCH • Need to verify format from SAM • Muon system has seen real inputs-CIC-SLIC • L1 format needs correction • Scint format OK but L2&timing interfere: errors • MDT format OK • PDT unformatted: October? • Current tests: • SCL_INIT for MBT-Alpha (for permanent MCH running) • Add 2nd channel of data (FIC-MBT-Alpha-VBD-L3) • real algorithms into SLIC; timing Fwd Mu already • Muon: 2nd or 3rd input: CIC-SLIC-MBT-Alpha-VBD-L3 • One event pushed through STT prototype vertical slice • FRC, STC, TFC: CTT roads, SMT clusters, fit

Arrival of L2 Inputs When inputs steadily available (subset, full) • L1 Trigger Mask to Global (August, October) • Cal (September?, November?) • Muon • Trigger (L2 software not tested) (June, November) • Detector (August,October?) • CTT,CPS (October,November) • FPS (November,December) • COOR programming September?

Online Software ( & Risks) • Alpha: • Much of structural software exists in simulation • Control/data flow for preprocessor and global • Loader and modified Linux kernel; • Developing drivers in EBSDK (fast turnaround); check in Linux • Draft drivers/setup for MBT and event loop • Some alpha firmware problems (PIO needed for A-W split) • SCL_INIT—in progress (complex) • VME driver, buffer allocation (OK) • Verify byte order etc to L3 • Error logging and beginnings of monitoring: testing • Linking, downloading to Worker; Linux 7.1 releases needed • Admin/Worker control; data flow software • few Alphas, so concentrate on 1-alpha crate for now • SLIC: • Basic operating system in place • monitoring; algorithms need download; scl_init

Online Software Plans Event data flow late Aug • Worker with filter code Sept • Multi-alpha (as available) Oct/Nov • interrupts for speed as needed Dec/Jan • Coor script downloading via TCC: Late Sept • Till then, configure from hand-edited file • Online and in TSIM • Data Flow Monitoring test Sept/Oct • Errorlogger to screen/S.E.S. Oct/Dec? • Global + Preprocessor Oct-Nov • FILTERING! (if have enough inputs…) • Verification: online vs. TSIM • 1st version running now; testing data capture • Needs pretty good data to be useful Oct/Nov?

Algorithms: in TSIM, downloadable; some L1SIM problems • Mu L1; Central alpha, DSP working, ready to download output fmts need update Fwd DSP in CVS; next release (alpha already there) • CTT base algorithm , tau working Tau tuning, slow movers waiting for postdoc hirewhen? • PS • CPS running in TSIM; needs better L1 • FPS written not released (no L1PS) when? • Cal all running in TSIM • e = Run 1B L1.5 • j merge needs work (interference with beta) • MET = L1for now • Global some running in TSIM now • e(cal,cps,track), j(cal); tracks; deta, dphi (e: fps-ready) • Ht, Mass, MET; rsep coming • Mu(with ctt), but no tau • Need Studies, Timing, Tuning! Lost 2 maintainers

Summary • Commissioning is underway in earnest • Some real inputs—need more to do physics • Mu, cal, ctt, cps is probable order • Most hardware in hand • Remaining alphas soon, I hope • Firmware written; commissioning it now • MBT, Alpha, FIC • Crucial scale-up tests in coming weeks • All hardware in crates • Multiple inputs • Algorithm downloads

Board Summary:Dates, Risks • SLIC January 2001 • Monitoring software • Crates/Power/Cables September • ORC; CIC crate • FIC September? • Commission; FPGA code problems? • MBT September? • FPGA code • Alpha now; September • Fragility of 4-6 from 1st production • PIO firmware • Fallback: Beta—next year • CIC,SFO August; September? • Install/Commission • Crate population, intra-crate cablingSeptember/October

Progress since Feb • Alpha • cards for commissioning; start final production • Fixed DMA; Beta started • FIC • Fixed output signal; FPGA work resumed • MBT • All firmware written/drivers (being debugged) • Integration testing with Alpha at 2 sites • multi-channel DMA, capture of SCL input info • CIC/SFO built • All power, most cabling • Software • Drivers for all devices written (being tested) • Most algorithms in TSIM • Real data sources in mu • data flow L1SCL to L3

Where do we put our Alphas?Staging; rotating tests; A+W Aug-Sept (5-10) • 1 Maryland • 2 Test Stand/UIC • 1-2 Global • 1-2 Mu/Cal (turns?) Oct-Nov (5 to20) • 2-4 Mu • 1-4 Cal • 1-2 Global • 2-5 CTT,PS • 1-2 Test stand • 1 Maryland/Va • 1-4 UIC/Test Stand

L2 Cards & Namesbuild/operate • FIC G-link to Hotlink Renardy, Mur (Saclay) Buehler, Kostas, Heinmiller (UIC) Kwarciany (FNAL) • MBT Hotlink, MBus, other I/O Giganti, Bard, Baden (Maryland) +Toole/ Schwienhorst • Alpha main processor (Campbell, Miller UM); Buehler,Heinmiller,Kostas, Varelas (UIC) Hirosky (UVa) Kwarciany/Zmuda (FNAL) • SLIC ProcessorSippach, Evans (Nevis/Columbia) Kothari, Christos (CU); Maciel, Fortner,Uzunyan(NIU) Christiansen, Strohmer, Trefzger, Schaile (Munich) • CIC, SFO SMB to RJ45 Hotlink; Hotlink fanout Lewis, Snow (Nebraska) Tester: Johns (UAZ) Hansen, Baldin, (Anderson) FNAL Maciel, Kothari, Fortner • VBD; Bit3 L3, TCC Zeller, Cutts; Commercial Mattingly (Brown); Schwienhorst (MSU)

Commissioning • Limiting factors: • Stable, fully functional L2 Cards (ouch) • MBT’s with full functionality • FIC: lack of on-site expertise • Lack of reliable system to modify firmware • Alpha: lack of firmware expertise on-site • Manpower (trained—getting better) • Big conflict with • Prototype testing (MBT, CIC, SFO) • Production debugging (Alpha) • Beta (fallback plan for Alpha) • Rick Kwarciany is part-time integration engineer • Alpha software for commissioning • Limited, in turn, by above problems • Availability of inputs • Real, or test; becoming limiting factor

Preprocessor Chains:Commissioning Scale ..20..40..60..80..100% • 0%Connectivity not tested • 20Signal compatibility demonstrated • 40Correctdata transfer once or usually; or physical layer (BIST?) full speed, error rate OK • 60Fake data, repeated transfers, error rate OK • 80Full speed fake data, error rate ok, >1 day • 100%Real data full cards, in system, full speed, errors OK, > 1 week

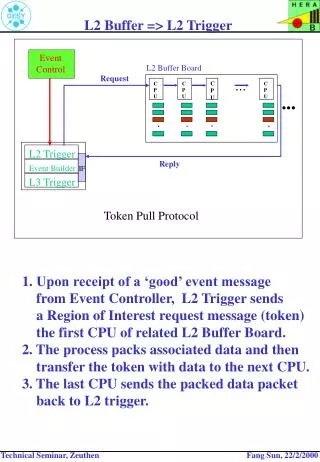

Preprocessor Chains 0%..20%..40..60..80..100% • L1DFE FIC..SFO MBT Alpha L3 (test stand) • L1Cal FIC SFO MBT Alpha VBD L3 (DAQ) • MuFE CIC SLIC SFO MBT Alpha L3 • Mutest CICSFOSLIC SFO MBT Alpha L3 • Alpha MBTMBT Alpha (2 crates) • Alpha Alpha • L1SCL MBT Alpha VBD L3 • MBT SFO patch panel MBTAlpha VBD L3 (test stand) • L1SCL MBT SFO SLIC MBT Alpha • L1FW FIC MBT Alpha • Alpha MBT L2FW ….