Predicting Chip Congestion & Layout Patterns for Better Electronic Design

Explore predicting congestion & layout patterns in chip design for efficient electronic device manufacturing. Improve connectivity prediction to avoid congested areas & find efficient layout search methods.

Predicting Chip Congestion & Layout Patterns for Better Electronic Design

E N D

Presentation Transcript

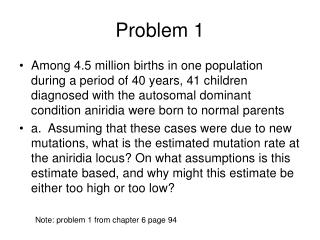

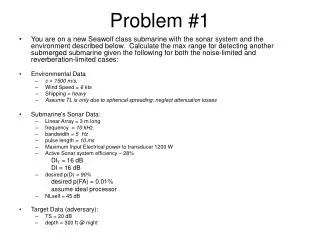

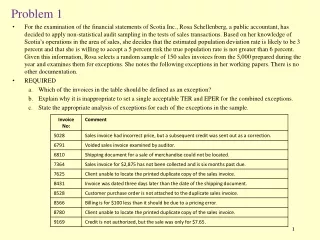

Problem 1 Defining Netlist Snarl Factor

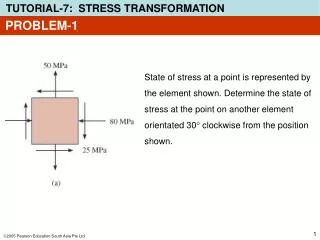

Blocks (e.g. AND,OR) Netlist == Graph Wires B D G A Outputs E Inputs C F H B D G B D G A F A F C E H C E H Some Background NB: Netlists are big ! > 4e7 blocks Placement Routing Congested area

Problem: Predicting Congestion • Predicting wire length, area early is essential • How fast will the chip go ? • How big must the chip be to allow all wires ? • Under predicting wires leads to congestion • Congested areas cannot be routed • The chip is in trouble • Can we define a better means of predicting congestion before placement and routing ? • Specifically can we define a localized connectivity metric and use it to partition a netlis

Real life congestion examples Congested area What we often get What we want

Snarl • Some netlists are easy to ‘un-snarl’ • Simple left to right logic • No / few loops • Uniform, low fan-out • Statistical models work • Easy to place and route • Some netlists are very difficult • E.g. ‘Crossbar Switches’ • Many loops • NB: not simple cycles or cliques • Non-uniform fan-out • Statistical models don’t work • Difficult to place and route

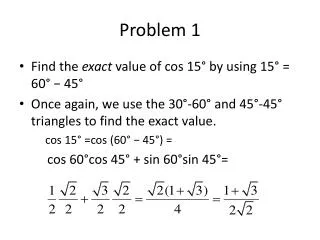

A A A A A A A A A A A A A A A A A TB =2 R=0 TB =4 R=0.5 A A A Internal Rents Rule • Used to predict the connectivity of ideal uniform netlists • P = TBBR • Where • P = number of external connections tothe partition • TB = average pins per block • B = number of blocks • R = Rent’s exponent • Think Gauss’s Law

Typical Rent’s Coefficients Ref: http://www.cedcc.psu.edu/ee497i/rents_rule.PDF

Challenge • Rent’s rule is used to predict connectivity of uniform netlists using empirical coefficients • Can we create a similar figure of merit metric on real, non-uniform netlists ? • Can we also localize the metric to portions of the netlist ?

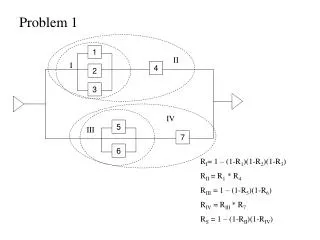

Example of New Metric U1 U2 U3 WhereU3 < U1 <U3 Uoverall = ƒ(U1 , U2 , … Un)

Possible Applications • Early identification of ‘difficult’ netlists • Early guidance towards netlist improvement • Better allocation of additional routing space

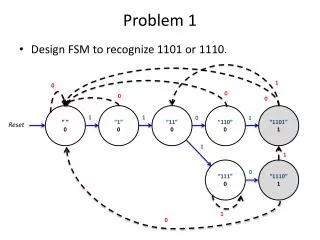

Problem 2 Geometric Pattern Recognition

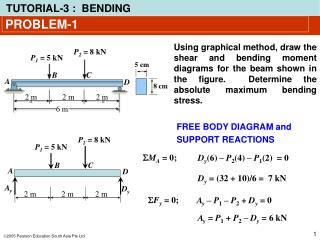

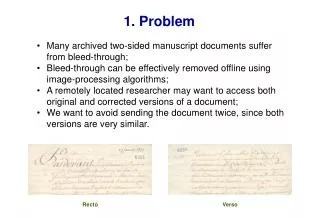

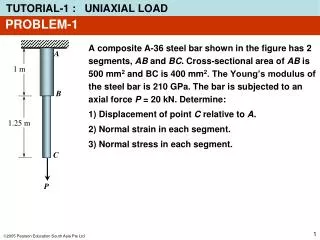

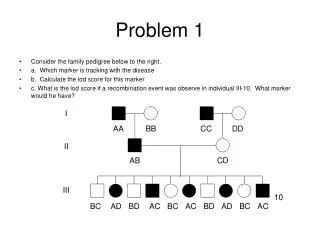

Some Background • Chips built up of many layers • Process similar to silkscreen • Devices composed of unique combinations of layer and geometry • Many steps analyze these geometric interactions • Manufacturability checks • Device and wire extraction • Yield calculations, etc. Diffusion Polysilicon gate Contact cuts

Problem: Finding Layout Patterns • Geometric interactions are quite complex • Modern chips have > 1e9 shapes • Some inter layer interactions matter, others do not • Relative geometric arraignment matters • Size and orientation (usually) do not • Most, but not all, shapes are rectilinear polygons • Methods exist to find general interactions by coding increasingly selective filters, but they are inexact and labor intensive • Can we define an efficient way to find all instances of a specific example sub-layout ?

Example: pattern recognition Find all occurrences of the sample layout in the chip

Challenge • What geometric representation best captures unique interactions between shapes ? • Can we find a representation that is invariant wrt. scaling and rotation ? • Can we find such a representation that can be searched very efficiently ?

Ideas • Can we transform both the chip geometry and the pattern into a graph of some type, then use sub-graph isomorphism techniques to identify the matches ? • If so ? What type of graph ? E.g Constraint graph.. X-graph How to couple X,Y ? Y-graph

Possible Applications Without OPC With OPC Optical proximity correction Layout migration