課程 2 -- 邏輯電路的 VHDL 語法

國立宜蘭大學電機工程系. 國立宜蘭 大學. 電機工程系. 課程 2 -- 邏輯電路的 VHDL 語法. 彭世興教師 編製. 國立宜蘭大學電機工程系. 1. 各種邏輯電路真值表 :. 國立宜蘭大學電機工程系. 國立宜蘭大學電機工程系. b. 輸出布林代數簡化 (1 之描述 ). a. 真值表. c. 邏輯電路描述. 國立宜蘭大學電機工程系. 2. 用邏輯電路完成真值表描述功能 :. b. 輸出布林代數簡化 (0 之描述 ). a. 真值表. c. 邏輯電路描述. 國立宜蘭大學電機工程系. a. 邏輯電路. b. 輸出布林代數簡化 (1 之描述 ).

課程 2 -- 邏輯電路的 VHDL 語法

E N D

Presentation Transcript

國立宜蘭大學電機工程系 國立宜蘭大學 電機工程系 課程 2 -- 邏輯電路的VHDL語法 彭世興教師 編製

國立宜蘭大學電機工程系 1.各種邏輯電路真值表:

b.輸出布林代數簡化(1之描述) a.真值表 c.邏輯電路描述 國立宜蘭大學電機工程系 2.用邏輯電路完成真值表描述功能:

b.輸出布林代數簡化(0之描述) a.真值表 c.邏輯電路描述 國立宜蘭大學電機工程系

a.邏輯電路 b.輸出布林代數簡化(1之描述) c. VHDL語法描述 y <= (notA AND B) or (A ANDnotB) ; 國立宜蘭大學電機工程系 3.邏輯電路的VHDL語法描述:

b.輸出布林代數簡化(0之描述) a.邏輯電路 c. VHDL語法描述 y <= (A or B) AND (notA ornotB) ; 國立宜蘭大學電機工程系

國立宜蘭大學電機工程系 4.範例:利用3個SW 開關選擇控制8個LED的亮滅 a. 板面規劃

國立宜蘭大學電機工程系 b. 內部功能真值表規劃 c.輸出化簡 (1之描述)

d.邏輯電路的實現 e. VHDL語法描述 LED0 <= notswa ANDnotswb ANDnotswc ; 國立宜蘭大學電機工程系

國立宜蘭大學電機工程系 5.ENTITY裡PORT的四種基本資料型態 • BIT 2. BIT_VECTOR(0 TO 7) 3. STD_LOGIC 4. STD_LOGIC_VECTOR(15 DOWNTO 7) STD_LOGIC,定義為: X: Forcing Unknown;浮接不定 0: Forcing 0 ;低電位 1: Forcing 1 ;高電位 Z: High Impedance;高阻抗 W: Weak Unknown;弱浮接 L: Weak 0;弱低電位 H: Weak 1 ;弱高電位 - : Don’t care ;不必理會 BIT,定義為: 0: Forcing 0 ;低電位 1: Forcing 1 ;高電位

陣列的資料型態 國立宜蘭大學電機工程系 ENTITY EX2 IS PORT (SW : IN STD_LOGIC_VECTOR( 2 DOWNTO 0 ); LED : OUT STD_LOGIC _VECTOR( 7 DOWNTO 0 ) ); END Ex2; ENTITY EX2 IS PORT (SW (0): IN STD_LOGIC; SW (1): IN STD_LOGIC; SW (2): IN STD_LOGIC; LED (0) : OUT STD_LOGIC; LED (1) : OUT STD_LOGIC; LED (2) : OUT STD_LOGIC; LED (3) : OUT STD_LOGIC; LED (4) : OUT STD_LOGIC; LED (5) : OUT STD_LOGIC; LED (6) : OUT STD_LOGIC; LED (7) : OUT STD_LOGIC ); END Ex2;

SW (2) : IN STD_LOGIC; SW (1) : IN STD_LOGIC; SW (0) : IN STD_LOGIC; 低位 高位 SW (2) SW (1) SW (0) SW (0) : IN STD_LOGIC; SW (1) : IN STD_LOGIC; SW (2) : IN STD_LOGIC; 高位 國立宜蘭大學電機工程系 低位 SW (0) SW (1) SW (2) 陣列的資料型態描述一 SW : IN STD_LOGIC_VECTOR( 2 DOWNTO 0 ) 陣列的資料型態描述二 SW : IN STD_LOGIC_VECTOR( 0 TO 2 )

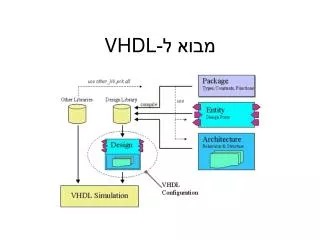

描述電路的特性 和運作 Architecture 宣告區 structure Description Dataflow Description Behavioral Description 結構性描述 資料流描述 (共時性處理) 行為性描述 (順序性 處理) 國立宜蘭大學電機工程系 6.ARCHITECTURE 架構三種描述法 VHDL電路架構的描述風格有三大類:

國立宜蘭大學電機工程系 7. 資料流描述(共時性處理) 訊號資料流動的描述,在VHDL 中有下列幾種描述: 1、直接式的訊號設定 “ <=” 2、條件式conditional 的訊號設定 “when … else” 3、選擇式Selected 的訊號設定 “with … select … when” 4、不完整的條件判斷指令“if … then …end if” ( 內部缺少了 ELSE 敘述) 5、完整的條件判斷指令“if … then … else … end if”

國立宜蘭大學電機工程系 b.條件式“when … else”的電路架構的描述 LED(0) <= ‘1’ when sel = “000” else ‘0’;

國立宜蘭大學電機工程系 3個SW 開關選擇控制8個LED的資料流描述 ARCHITECTUREbehaviorOF ex2 IS BEGIN LED (0) <= ‘1’ when sel = “000” else ‘0’; LED (1) <= ‘1’ when sel = “001” else ‘0’; LED (2) <= ‘1’ when sel = “010” else ‘0’; LED (3) <= ‘1’ when sel = “011” else ‘0’; LED (4) <= ‘1’ when sel = “100” else ‘0’; LED (5) <= ‘1’ when sel = “101” else ‘0’; LED (6) <= ‘1’ when sel = “110” else ‘0’; LED (7) <= ‘1’ when sel = “111” else ‘0’; END behavior;

國立宜蘭大學電機工程系 利用3個SW 開關選擇控制8個LED的亮滅

國立宜蘭大學電機工程系 vhd程式檔

國立宜蘭大學電機工程系 ucf接腳定義檔