HDL Bencher

250 likes | 418 Views

HDL Bencher. FPGA Design Workshop. Objectives. After completing this module, you will be able to: Describe the process to create a testbench for HDL designs Reduce testing time by integrating HDL Bencher into Digital Design Labs. Outline. Overview Create a New Source Create Waveforms

HDL Bencher

E N D

Presentation Transcript

HDL Bencher FPGA Design Workshop

Objectives After completing this module, you will be able to: • Describe the process to create a testbench for HDL designs • Reduce testing time by integrating HDL Bencher into Digital Design Labs For Academic Use Only

Outline • Overview • Create a New Source • Create Waveforms • Export Testbench • Summary For Academic Use Only

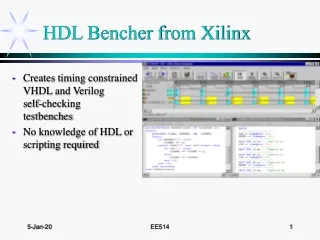

HDL Bencher • Creates timing constrained VHDL and Verilog self-checking testbenches • No knowledge of HDL or scripting required For Academic Use Only

Overview • HDL Bencher helps validate design function and performance • HDL Bencher generates • VHDL or Verilog testbenches • Design specific waveforms • Documentation • Testbenches can be simulated with various simulators • Model Technology • Synopsys For Academic Use Only

Advantages • No HDL or scripting knowledge required (or even needed!) • No need to manually modify testbenches for each design revision For Academic Use Only

How It Works • Step 1: Create New Source • Step 2: Draw stimulus and response waveforms • Step 3: Export testbench For Academic Use Only

Outline • Overview • Create a New Source • Create Waveforms • Export Testbench • Summary For Academic Use Only

Create a New Source For Academic Use Only

HDL Bencher • Unit under test is analyzed, when selected • Port problems • Syntax violations • Inconsistencies • Design timing selected • Specify clock timing • Single, multiple, or internal clocks For Academic Use Only

HDL Bencher For Academic Use Only

Title bar Process bar Port direction Line numbers Menu Waveform window Waveforms HDL source editor HDL Bencher Windows For Academic Use Only

Outline • Overview • Create a New Source • Create Waveforms • Export Testbench • Summary For Academic Use Only

Create Waveforms • Data values • 1, 0 ,X ,Z, U • Assignments • Double-click bit signal to toggle value • Pattern wizard assigns a range of cell values • WaveTable assign signals like a spreadsheet • By default, decimal values are shown in the WaveTable • Waveform values are checked as they are entered • Validation check for non-binary inputs only (for example, hex, or decimal) For Academic Use Only

Toggling • Toggling bit values is the easiest way to assign bit signals • Simply click directly on the signal’s waveform at the time where changes should take place Click directly on these boxes, at the time where signals should toggle For Academic Use Only

WaveTable • Intended for fast behavioral verification • Waveforms represented as cells • Data entered in spreadsheet format • Double-click a signal at the time it should be changed, to access value cell editor • Enter value and press Return for the next time frame • Range validation checked after each entry Double-click in this area Enter values in this area For Academic Use Only

Pattern Wizard • Aids complex waveform input • To access, click a signal at the time it should be changed to access value cell editor • Note: light blue background = input assignment, • light yellow background = output assignment Click in this area Click here for Pattern Wizard For Academic Use Only

Available patterns Pattern description Changes depending on the pattern selected Count unit in clock cycles Pattern Wizard For Academic Use Only

Outline • Overview • Create a New Source • Create Waveforms • Export Testbench • Summary For Academic Use Only

Testbench • Translates waveforms to testbenches • Writes out VHDL or Verilog testbench • Color-coded for easy reading and reference • Includes • Library extractions • Log file creation • Procedure check • Input assignments • Output validation • Defined test signals • Delay verification • UUT (Unit Under Test) instantiation For Academic Use Only

VHDL compliance Configuration • Options Configuration • Ability to automatically terminate the testbench for export on the last assignment For Academic Use Only

Testbench • Waveform file extensions are TBW • Waveform file can be seen in the Sources in Project window of the Project Navigator • To view testbench: • In Sources in Project Window, select the TBW file • Then in the Processes for Current Source window, click View Behavioral Testbench For Academic Use Only

Outline • Overview • Create a New Source • Create Waveforms • Export Testbench • Summary For Academic Use Only

Summary • HDL Bencher helps validate design function and performance • The three steps to create a testbench are • Create a new source • Develop waveforms • Export testbench • Writes out VHDL or Verilog testbench For Academic Use Only

Where Can I learn More? • The HDL Bencher tool • Help Menu • support.xilinx.com software manuals Development System Reference Guide HDL Bencher Help For Academic Use Only