PLL

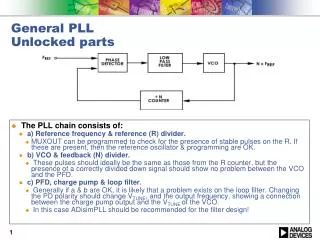

TEORIA de CIRCUITOS. PLL. Lazo de Enganche en fase (Phase locked Loop). PLL (Phase Locked Loop). La función de un PLL es la de “enganchar” la frecuencia del VCO a la frecuencia de la señal de entrada. f in. Comparador de Fase. Filtro Pasabajos. V o. VCO. f vco. PLL.

PLL

E N D

Presentation Transcript

TEORIA de CIRCUITOS PLL Lazo de Enganche en fase (Phase locked Loop) Cátedra de Teoría de Circuitos - 2005

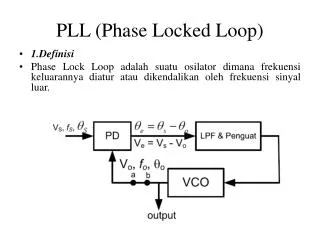

PLL (Phase Locked Loop) La función de un PLL es la de “enganchar” la frecuencia del VCO a la frecuencia de la señal de entrada fin Comparador de Fase Filtro Pasabajos Vo VCO fvco PLL Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase La función del comparador de fase es la de entregar una tensión proporcional a la diferencia de fase entre la señal del VCO y la señal de entrada fin Comparador de Fase fvco Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase Implementación 1: Multiplicador fin fvco Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase Implementación 1: Multiplicador Lazo enganchado en cuadratura La ganancia del detector es máxima en pi/2 Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase Implementación 2: XOR T La salida contiene una frecuencia doble a la original + la continua. thi Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase VCO Ref Up Dn Implementación 3: Edge Detector (Phase Frequency Detector) Estos detectores son sensibles solo a los flancos y por lo tanto no dependen del DC de la señal. Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase Vi rising edge Vi rising edge Vi HI-Z Source Current Sink Current V0 Charge Pump Tri-State V0 rising edge V0 rising edge Implementación 4: Edge Detector + Charge Pump V0 is late Pump Up V0 is early Pump Down Vi Cátedra de Teoría de Circuitos - 2005

Comparador/Detector de fase Análisis del PFD + Charge Pump Suponiendo que Vi y V0 son de igual frecuencia y que el flanco de Vo aparece un tiempo después del flanco de Vi tenemos dos posibilidades: En este caso ambas señales están sincronizadas en frecuencia y en fase y por lo tanto no existe salida en el detector. La salida estara cargando al capacitor durante un tiempo por cada periodo de la senial Vi. Si el periodo de la senial Vi es Ti entonces el valor medio de la salida del Charge and Pump sera: La constante se introduce para convertir retardo temporal en un retardo de fase. Notese que el retardo de fase deberá ser a lo sumo Ti. Cuando la fase es la corriente suministrada sera mientras que cuando es la corriente absorbida sera – y por lotanto la ganancia del detector sera : Cátedra de Teoría de Circuitos - 2005

VCO La función del VCO es generar una frecuencia proporcional a la tensión de entrada. VCO Free Running El VCO es un integrador Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) fin Vo PLL Transferencia Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Transferencias fin PLL Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Transferencias Vo fin PLL Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Rangos de captura y enganche Cátedra de Teoría de Circuitos - 2005

Low Pass PLL (Phase Locked Loop) Transferencias Teorema del valor final Como Tracking !!! Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Transferencias En Ausencia del filtro F(s): • El proceso de captura es mas lento • El rango de captura decrece • Mejora el rechazo a las perturbaciones • Respuesta sobre amortiguada Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Filtros de primer orden Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Filtros de primer orden Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Filtros de primer orden Activo Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) Síntesis de frecuencias Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) PLL CD4046BC Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) PLL CD4046BC Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) PLL CD4046BC Cátedra de Teoría de Circuitos - 2005

PLL (Phase Locked Loop) PLL CD4046BC Cátedra de Teoría de Circuitos - 2005