FUNCTIONAL OVERVIEW

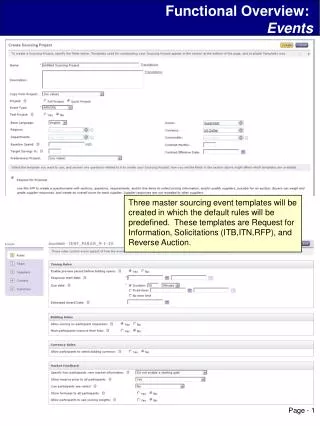

FUNCTIONAL OVERVIEW. Design a synchronous 4-bit up and down counter Operates at 25MHz on the positive edge of the clock Designed to drive a 10pF capacitive load Latches a valu e at any point by toggling the enable. COUNTER DESIGN FLOW. COUNTER. COMBINATIONAL LOGIC. T_FLIP_FLOP.

FUNCTIONAL OVERVIEW

E N D

Presentation Transcript

FUNCTIONAL OVERVIEW • Design a synchronous 4-bit up and down counter • Operates at 25MHz on the positive edge of the clock • Designed to drive a 10pF capacitive load • Latches a valu e at any point by toggling the enable

COUNTER DESIGN FLOW COUNTER COMBINATIONAL LOGIC T_FLIP_FLOP SCHMITT TRIGGER SUPER BUFFER D FLIP_FLOP XOR

Schmitt Trigger Design • Designed For: • VTH(LH) of 3V • VTH(HL) of 2V VTH(LH) VTH(HL)

Super Buffer Design (Assumed 4 stages) • Design First Stage Inverter With Symmetric delays • Calculate Ratio Wp/Wn • For Each Successive Stage: (Where N is the Nth Stage) • α^N(Wp/Wn)

French Fried Design • I(max) for AL (Metal 1) = 1 x 10^5 A/cm^2 • Our Buffer: 5.27 x 10^5 A/cm^2

T-Flip Flop Schematic Preset Clear Clock Enable

Conclusion • 4 Bit Counter with up and down count capability • Preset, Clear, Enable Inputs • Operates at 25Mhz Clock Frequency with a delay of 6ns from Super Buffer. • Input Noise Immunity 2.5V +/- 20% • Output power of 60mW Driving 10pF Load • Total Area of 406um x 925um = 3.76e-3cm^2