Software Defined Silicon

Software Defined Silicon. 晶片功能的軟體化. Presented By. 謝啟東 五子五 (1979) MSCS , Vanderbilt (1985) 副總,銳力科技 黃模淼 五子五 (1979) MSEE ,交大光電 副總,銳力科技. Agenda. Overview 30 min Software Defined Silicon 50 min Break 5 min Demo 20 min Q & A 10 min. Overview.

Software Defined Silicon

E N D

Presentation Transcript

Software Defined Silicon 晶片功能的軟體化

Presented By 謝啟東 五子五 (1979) MSCS,Vanderbilt (1985) 副總,銳力科技 黃模淼 五子五 (1979) MSEE,交大光電 副總,銳力科技

Agenda • Overview 30 min • Software Defined Silicon 50 min • Break 5 min • Demo 20 min • Q & A 10 min

Buy a Product Best Cheaper Easy to Use (User-Friendly)

Product Development Steps System Integration

Product Spec / Functions Cost Price Time Time to the Market BOM Cost

積體電路的變革 Shorter Development Time & Cheaper BOM

Product Market Volume Market Niche Market Big Volume Competitive & Bloody Small Volume Less Competitive ASIC ASSP Standard Solution Glue Logic Programmable Devices Non-Standard Solutions

To Design a Product ? Glue Logic ASIC / ASSP Programmable ICs Modules Solution Boards… Time to the Market BOM Cost By Hardware By Software

Trade-Off ASIC / ASSP FPGA / CPLD Cheaper Easier Specific Expensive Complicate Flexible By Hardware By Software Expensive Better Performance Cheaper Performance?

ASIC / ASSP Application Specific IC Designed to Perform the Specific Function VGA Chips Keyboard Controller Mouse IC DVD Chips 3G Chips Wi-Fi Chips Its Specific Function cannot be Changed or Programmed

Programmable ICs Programmed for Functions : Flexible PAL / GAL Programmable Array Logic Gate-Based xROM x Read-Only Memory Hard-Wired CPLD Complex Programmable Logic Device FPGA Field-Programmable Gate Array Functional Block uC Micro-Controller CPU-Based

Programming a Devicefor a Function PAL / GALBoolean Equation by PAL Programmer ROM Programmer CPLD JTAG Port (Joint Test Action Group) Proprietary In-Circuit Programmer FPGA JTAG Port by Proprietary In-Circuit Programmer + Proprietary Languages uCProgrammer + Languages

Any Silicon Which Its Function Can Be Easily and Flexibly Defined by CPU-Based High-Level Languages

Software Defined Silicon Programmed by High-Level Language Flexibly Define a Silicon’s Function

Software Defined Silicon

What’s SDS? Processor Processor Processor Program Code

Why SDS? The Fact… Fast tune-cycles and market change “Scale” grows up exponentially How do you differentiate ? “Loading” & “risk” rises up Processor… Powerful Reliable Economic

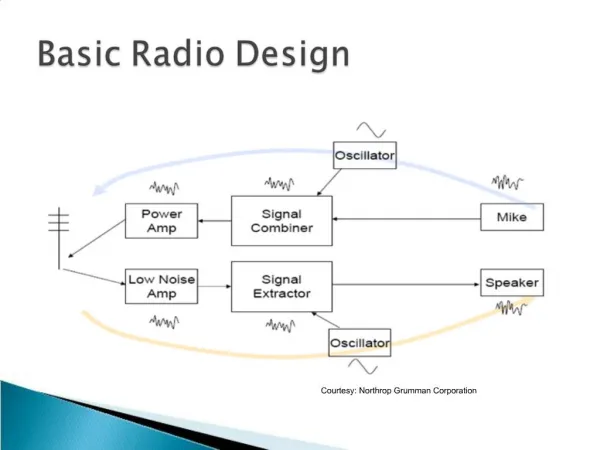

What SDS should be? Direct & programmable I/O access Programmable timing control Highly responsive processing Independent & wide processing path Inter-connection channel Reliable & convenient development tool Is It Possible ??

Yes, Here is an example… 8K OTP 64K SRAM 400MHz RISC Processor 8 threads per core Up to 64 I/O pins

The advanced I/O I/O Ports are tightly coupled to the core Dedicated instructions for I/O port assignment Has the concept of timing and may be synchronized to an internal reference clock or an external input clock

For “Timing” In each core, Ten 100MHz timer public resource are available for any thread. (10 ns resolution) “Timer” may link up with any event on I/O port and inter-communication channel.

Flexible “Processing Path” Eight independent threads in one core Dedicated instruction for thread job assignment Proprietary compiler to ensure 50 ~ 100 MIPS on each thread Xlink switch are available for each thread to enable threads be parallel and/or serial chained processing

Xlink Switch for inter-connection Use “chan” to connect two “chanend” “chanend” threads may be on same core, different core or different chip.

Design Flow Software design and debug flow is similar to other embedded tool chains – Focus on C/C++ Adds language support to simplify tasks relating to concurrency and real-time control – XC Complete set of tools from design capture to advanced debugging Accessible both online or on your desktop machine using downloadable tools A lot of design template are available for reference

What’s XC XC looks and feels like C Support for : • I/O with timing • Communication • Event • Multiple threads and cores

The new concept for engineers Thread may be “Software task”, “Timing I/O”, “Data processing”, “State machine” System job partition Using threads as building blocks

SDS usage Scenarios Intelligent Bridge I/O expansion or companion chip SDS based ASSP

A workable example -- Real-time Audio Filter with Ethernet AV input

Designing with SDS - 1 Toggle an LED and write a UART transmit function in XC: • Focus on: • • ports • • timers

Designing with SDS – 1 (Cont.) Step1 : Define BAUD_RATE & BIT_TIME Step2 : Declare output ports for LED & TxD Step3 : Use one Timer in main() routine to flash LED & send message to UART Txd port periodically Step4 : Use another Timer resource on transmit() routine to control bit timing on UART port

Summary : SDS is possible indeed. Using threads as building blocksof system Pending issue • Is it possible to achieve Gbit/sec? • How compiler work ? • Competitive ? • Other ?