FPGA Programming in LiCAS: ADC for Continuous Data Readout Week 8 Report

Detailed report on programming FPGA in LiCAS for ADC data readout. Progress, test function completion, data formatting, error decoding & simulation. Real data testing & diagnostics for bugs.

FPGA Programming in LiCAS: ADC for Continuous Data Readout Week 8 Report

E N D

Presentation Transcript

Programming of FPGAin LiCAS ADC forContinuous Data ReadoutWeek 8 ReportFriday 22nd August 2008Jack Hickish

Progress Last Week New Test Function completed Error decoding/formatting program almost completed

Since then... Simulating Data Generated pattern 0,2,4,6, 0,2,4,6, ... Averaged over 4. Output: 3,3,3, ... Tested again with other averages and sampling. Conclusion: New accumulators working.

Formatting Data Data written out in raw binary for speed. Decoded and reformatted into columns Including error notification and column realignment after data lost. Tested and working! Then not working! (Could be problem with FPGA software)

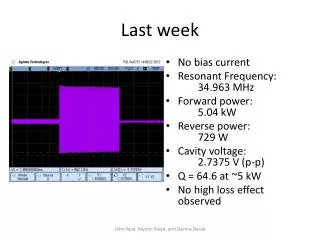

Real Data Connected to LiCAS short & long amplifiers Sinusoidal (ish) background seen on short amplifier. Voltage ranges appear to be misaligned. But encouraging.

Speed Test Overnight 3 channels full speed (~17MB/s) At time of writing about 360GB of data should have been generated. Will try to check for errors today, but likely something will crash or catch fire from the strain.

Diagnostics Bug First 3 pieces of data from an acquisition run show FIFO full. Thought it was caused by full flag flashing on reset, so built in a delay before flag checking starts. Hasn't helped (and may have broken something else) To Do...

The Day Ahead... • Fix error checking and/or decoder • Check speed test for errors.