Interrupts

Interrupts. Chapter 8 – pp 209-214 Chapter 10 – pp 258-264 Appendix A – pp 537 & 543-545. Interrupts & Exceptions. Interrupts: - Asynchronous external requests for service (think device, like keyboard or printer, needs service).

Interrupts

E N D

Presentation Transcript

Interrupts Chapter 8 – pp 209-214 Chapter 10 – pp 258-264 Appendix A – pp 537 & 543-545

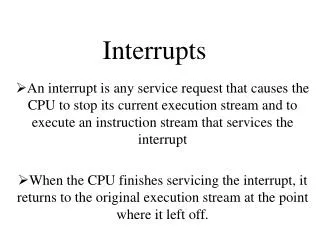

Interrupts & Exceptions Interrupts: -Asynchronous external requests for service (think device, like keyboard or printer, needs service). - Being asynchronous, Interrupts can occur anyplace in your program! -They are a normal event, and shouldn’t interfere with the normal running of your program. Exceptions: -“Synchronous” internal requests for service based upon abnormal events (think illegal instruction, illegal address, overflow, hardware malfunction, or …). - Being synchronous, Exceptions occur when there is abnormal event in your program (like divide by zero, or illegal memory location)! -They are abnormal events and often result in the termination of a program, or the execution of a “recovery” before continuing. LC-3 Interrupt/Exception Vector Table: (256 Address Vectors) -x0100 – 017F: Used for addresses for Exception service routines. Vector # is provided by the CPU. -x0180 – 01FF: Used for addresses for Interrupt service routines. Vector # is provided by a Device.

Program Context • Every task (Computer Program) has a Program Context. • The Program Context is the set of values of all the program “state variables” at a specific point: • at the end of the execution of a program machine level instruction. • it is everything that must be known to continue to execute the program correctly. • The Program Context includes: • PC • SP • PSW (supervisor/user mode, Priority, Condition Codes) • Values of all variables i.e. data – general registers and memory (including the stack)

Program Context Implications • What are the Program Context implications of: • Executing a Trap Routine ? • Executing a Subroutine (or Function, or Method) ? • Executing an Interrupt ?

Program Context Implications What are the Program Context implications of: • Executing a Trap Routine ? • The PC must be saved and restored (Done by TRAP & RET) (Registers must be restored by Trap Routine - It is assumed all other “state” values effectively remain unchanged) • Executing a Subroutine (or Function, or Method) ? • The PC must be saved and restored (Done by JSR or JSRR, & RET) (Registers must be restored by Trap Routine - It is assumed all other “state” values effectively remain unchanged) • Executing an Interrupt ? • The PC, SP, & PSW must be saved and restored (Done by Supervisor & RTI) (Registers must be restored by Interrupt Service Routine - It is assumed all other “state” values effectively remain unchanged)

Program Context Includes: PC, PSW (PSR), & SP (R6) Program Status Word:(in the Program Status Register) PSW (PSR):PSR[15] – Privilege Bit - 0 for Privileged (Supervisor) State 1 for User State PSR[10:8] – Priority Bits - Eight Levels (7 is the highest) PSR[2:0] – Condition codes - N, Z, P Stack Pointer: ( [R6] = USP or [R6] =SSP ) USP & SSP: User Stack Pointer & Supervisor Stack Pointer USP.saved & SSP.saved: Two auxiliary registers that are used to store the value of the Stack Pointer (User or Supervisor) that is not in use. This is done automatically when the PSR[15] bit is switched. -When in User Mode (PSR[15] = 1), R6 is the User Stack Pointer and SSP.Saved contains the Supervisor Stack Pointer. -When in Supervisor Mode (PSR[15] = 0), R6 is the Supervisor Stack Pointer and USP.Saved contains the User Stack Pointer.

Interrupt Components Device (Keyboard shown here as example)Memory Keyboard Status Register: Keyboard Data Register: Keyboard Priority: 0 to 7 Device Interrupt Vector #: 180 to 1FF (Note: device actually sends 00-FF to CPU) CPU PC (Program Counter) R6 (Stack Pointer) PSR (Program Status Word) Bits: 15 10 9 8 2 1 0 |S||Priority|| N| Z| P| USP.saved (User Stack Pointer Storage) SSP.saved (Supervisor Stack Pointer Storage)

Interrupt Example Intr Vectors Supervisor Stack Program flow

Interrupt Process This is important to understand ! An interrupt can occur “anywhere” in a computer program, unlike Trap Calls or Subroutine Calls which occur exactly where you place them ! 1) Programmer Action: Loads a Service Routine for the Device, and enters its Entry Addr in the Interrupt Vector Table Enables Interrupts by setting “intr enable” bit in Device Status Reg 2) Device Action to Request an Interrupt: When device needs service, (done or ready bit set, and interrupt enable bit set) and - its priority is higher than the priority of the Presently Running Program, and - execution of the present instruction is complete, then The Device submits an “Interrupt Request”, and when granted, supplies CPU with Interrupt Vector # 3) CPU Action to Initiate Service of the Interrupt: When the CPU accepts the Interrupt Request (Priority higher than the present program Priority) - The CPU goes into Privileged Mode (PSR bit 15 cleared) - [R6] USP.saved register and [SSP.saved] R6, the stack pointer - The Processor saves the “state” (context) of the program (must be able to return) The [PC] and the [PSR] are PUSHED onto the Supervisor Stack (Other regs are not. Why?) - Priority level is set (established by the interrupting device) and the CC’s are cleared Then, thePC is loaded with the service routine address (between 180 and 1FF). (Based upon the Device supplied Interrupt Vector #: 00 to 7F) 5) Interrupt Service Routine is Executed: - Done or Ready bit is reset in the Device SR (Likely, it reads from or writes to the Device DR) (This is done so that another interrupt is not generated before the present one is serviced) - Ends with an RTI 6) RTI Initiates Return of Control to the Interrupted Program: - The stored User PSW is POPed into the PSR, and the User PC is POPed into PC), - (R6)SSP.saved, (USP.savedR6), - and then the next instruction in the interrupted program is fetched.

Interrupt Driven Keyboard Service Routine Program: • Program consists of a main program and a keyboard service routine. • Program will Print “Input an Endless Character String “ and loop forever. • Program Organization: main program: “Create Stack” Load address of your service routine into the Interrupt Vector (address x0180) Print a prompt message Set up the Keyboard to be able to Interrupt (set Status Register bit 14) Loop service routine: Read keyboard data register (resets the ready bit (bit 15)) Echo the char to the Monitor (using polling) Execute an RTI instruction at the end of the routine