32-bit Pipelined RISC Processor

32-bit Pipelined RISC Processor. Group 1. aka “Go Us”. CS m152b TA: Young Cho Lab section 1. Alice Wang Ann Ho Jason Fong. IF/ID. ID/EX. EX/MEM. MEM/WB. Register File. PC Control. ALU. Data Memory. Instruction Memory. General Review of a Pipelined Processor.

32-bit Pipelined RISC Processor

E N D

Presentation Transcript

32-bit Pipelined RISC Processor Group 1 aka “Go Us” CS m152b TA: Young Cho Lab section 1 Alice Wang Ann Ho Jason Fong

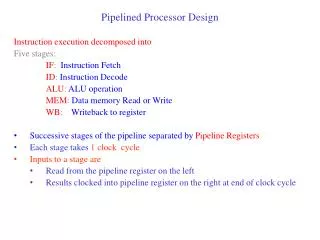

IF/ID ID/EX EX/MEM MEM/WB Register File PC Control ALU Data Memory Instruction Memory General Review of a Pipelined Processor

Memory Controller Design Design challenge: 32-bit processor with 16-bit memory interface • One every memory access, need to make two memory accesses in order to get a 32-bit word out of a 16-bit memory interface. Solution: Clock memory controller twice as fast as rest of processor • Effectively makes a memory access on the rising and falling edge of the processor’s clock cycle • Each processor clock cycle corresponds to two clock cycles of the memory controller • This allows two memory accesses per processor clock cycle

31 28 27 25 24 22 21 19 8 4 3 0 31 28 27 25 24 22 15 0 31 28 15 0 Instruction Format R-type instruction opcode rs rt rd shamt funct I-type instruction opcode rs rt imm16 J-type instruction opcode imm16

Parallel Multiplier (more efficient, but more hardware) x4 x3 x2 x1 x0 y0 y1 y2 y3 y4 z9 z8 z7 z6 z5 z4 z3 z2 z1 z0

Forward From ALU output Forward From memory output ID/EX EX/MEM MEM/WB Data Forwarding

PC Adder 1 Hold PC value Insert NOP NOP IF/ID Hardware NOP Insertion

Data Forwarding and Stall Insertions:Observed Results Sample program: Bubble-sort 6 numbers Assembler insertion of NOPs for data hazards and branch/jump delays Machine code size: 66 words of memory Execution time: ~750 clock cycles Hardware data forwarding and stall insertion: Machine code size: 35 words of memory Execution time: ~400 clock cycles

Conclusion Still cooking something up… We conclude that we do not know what to conclude.

References • Hennessey and Patterson, Computer Organization and Design (2nd Ed.), 1998, pages 476-495 • Donaldson, John L., “Pipeline Hazards”, http://occs.cs.oberlin.edu/faculty/jdonalds/317/lecture08.html • Ercegovac, Intro To Digital Systems