First test results from a Shield-Less Hybrid Module

40 likes | 146 Views

The first test results from a shield-less hybrid module show improved performance with lower mass and thinner build compared to previous designs. The hybrid uses blind vias, resulting in a 4-layer build. Notably, the Double Trigger Noise (DTN) measurements indicate no patterning in the occupancy, a significant improvement. While encountering a failed via and a break on the COM line, solutions have been implemented to address these issues. Quality assurance processes are in place for the vias, with plans to monitor their resistance evolution through thermal cycling tests. The successful testing of the shield-less hybrid module paves the way for future improvements in circuit design and assembly processes.

First test results from a Shield-Less Hybrid Module

E N D

Presentation Transcript

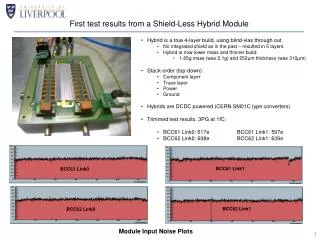

First test results from a Shield-Less Hybrid Module • Hybrid is a true 4-layer build, using blind-vias through out • No integrated shield as in the past – resulted in 5 layers • Hybrid is now lower mass and thinner build: • 1.65g mass (was 2.1g) and 250µm thickness (was 310µm) • Stack-order (top-down): • Component layer • Trace layer • Power • Ground • Hybrids are DCDC powered (CERN SM01C type converters) • Trimmed test results, 3PG at 1fC: • BCC61 Link0: 617e BCC61 Link1: 597e • BCC62 Link0: 608e BCC62 Link1: 639e BCC61 Link1 BCC61 Link0 BCC62 Link1 BCC62 Link0 Module Input Noise Plots

Double Trigger Noise • Recap – results from prototype shield-less hybrid showed a regular patterning in the occupancy – but only on outer strips • Problem traced to noise injection from vias attributed to COM and L1A traces on hybrid • Vias are thru-hole they ‘punch through’ the ground layer • Affects outer strips only due to the hybrid being glued asymmetrically w.r.t. sensor strips DTN at 1fC for prototype hybrid showing patterning in occupancy • New shield-less hybrid results • DTN shows zero occupancy until 0.5fC, (see plot below) – no evidence of patterning • Though one chip does show increased occupancy • Chip shows higher gain compared to the rest, also seen at hybrid test – But not at Wafer Probing • Even with the ‘bad’ chip the occupancy is very low Summed hits: 2 Suspect chip? Summed hits: 8 Summed hits: 27 Summed hits: 4

What else did we learn? • Encountered a failed via on one of the hybrids • Never before encountered such failures with previous circuits – used through-hole and not blind vias • Circuits are shipped electrically perfect from vendor • Assume failure occurred during reflow stage of passive attachment? • Problem identified with break on the COM line to a single chip • Fix was to add a bond wire to bridge the break • Plated Through Hole QA is built into hybrid panels • 3 groups of via daisy chains are resident on the panel • Each group made up of ~15% total drilled holes • Tests conductivity between L1-L2, L1-L3 and L1-L4 • Plan to thermally cycle ‘spare’ panels and see how resistance of chains evolves • If failures are encountered plan is to feedback results to vendor to see how to address the issue 3 groups of via chains

Summary • First true Shield-Less hybrid module has been shown to work electrically very well • Input and Double Trigger Noise (DTN) results are excellent • Critical DTN measurement shows no patterning in the occupancy (as seen on previous prototype shield-less hybrids) • Caveat is problem encountered with a single failed via on one circuit • Never seen before with previous hybrids using through-hole technology and not blind-vias • Via QA is built into panel • Plan to thermally cycle panels to check quality of via chains after each thermal cycle • Failures encountered will be fed-back to the vendor for advice • For ABC130 the default will be to build the circuits without a shield