USART Peripheral Interfac e Modo UART

USART Peripheral Interfac e Modo UART. USART :U niversal Synchronous / asynchronous receive/transmit. Sincrónico (SPI). Asincrónico (UART). UxCTL Usart Control Register. Modos seriales USART. Esquemático USART. Varios protocolos de comunicación. Datos de 7 ó 8 bits.

USART Peripheral Interfac e Modo UART

E N D

Presentation Transcript

USART Peripheral InterfaceModo UART USART:Universal Synchronous/asynchronous receive/transmit

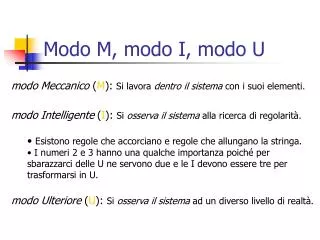

Sincrónico (SPI) Asincrónico(UART) UxCTL Usart Control Register Modos seriales USART

Varios protocolos de comunicación Datos de 7 ó 8 bits Tx y RxdeLSB primero Buffers de Tx y Rx separados Registrosde desplazamiento de Tx y Rx Algunas Características

Capacidad de salir de modo bajo consumo, dado un cambio de estado Tasa de transmisión programable Flags de detección y supresión de errores Interrupción independiente para Rx y Tx Algunas Características

Operación Inicialización y reinicio (reset) Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de transmisión Generación de tasa de transferencia Interrupciones

PUC SWRST=1 UxCTL Usart Control Register Inicialización y reinicio (reset)

Operación Inicialización y reinicio (reset) Formato del Character Formato del Character Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de transmisión Generación de tasa de transferencia Interrupciones

Octavo bit de dato Adress bit Bit de paridad Segundo bit de detención Formato del character

Operación Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de transmisión Generación de tasa de transferencia Interrupciones

Bit MM=0 Idle-Line Multiprocessor Format 2 dispositivos Address-Bit Multiprocessor Format Bit MM=1 3 o más dispositivos Protocolos de Comunicación

Tiempo de espera de 10 bits o mas Expandido Frame Frame dentro del bloque Primer Frame dentro del bloque es uan direccion, sigue a un tiempo de espera Frame dentro del bloque Tiempo de espera menor a 10 bits Protocolos de Comunicación: Protocolos de Comunicación:Idle-Line Multiprocessor Format

TXWAKE=1 Escribir character en UxTXBUF Contenido de UxTXBUF es llevado al registro de TX Transmite 11 unos TXWAKE=0 automaticamente Protocolos de Comunicación Idle-Line Multiprocessor FormatTransmisión de datos

Se escribe la dirección en UxTXBUF Registro tiene que estar listo Se inicia la transmisión con un character ‘dont care’ Protocolos de Comunicación: Idle-Line Multiprocessor FormatTransmisión de datos

Bloques de frames Tiempo de espera Expandido Primer frame del bloque es una dirección AD Bit es cero para dato en el bloque Tiempo de espera Protocolos de Comunicación: Protocolos de Comunicación:Address-Bit Multiprocessor Format UxRCTL Usart Receive Control Register

Se escribe en bit TXWAKE Este es cargado en el address bit del carácter transferido Se limpia automáticamente UxTCTL, Usart Transmit Control Register Address-Bit Multiprocessor Format Protocolos de Comunicación: Control del address bit para transmisión

Operación Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Detección automática de errores Detección automática de errores Habilitación de recepción Habilitación de transmisión Generación de tasa de transferencia Interrupciones

UxRCTL Usart Receive Control Register Detección automática de errores herores Error de framing Error de paridad Error de rebalse (receive overrun) Condición de break

Operación Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de recepción Habilitación de transmisión Generación de tasa de transferencia Interrupciones

URXEX Habilita o deshabilita recepción de datos Se guardan en el UxRXBUF Habilitación de recepción Habilitación de recepción (Receive Enable)

Bit de inicio inválido Incompleto URXEx=0 URXEx=1 Condición de Interrupción Estado de espera (Recepcion Deshabilitada) URXEx=1 Receptor recibe el character Recepcion Deshabilitada Character recibido URXEx=0 URXEx=1 URXEx=0 UxTCTL, Usart Transmit Control Register Habilitación de recepción Habilitación de recepción (Receive Enable)

Operación Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de transmisión Habilitación de transmisión Generación de tasa de transferencia Interrupciones

UTxEX habilita o deshabilita transmisión de datos Se inicia la transmisión escribiendo en UxTxBUF Habilitación de transmision Habilitación de Transmisión (Transmit Enable)

No se escribe dato en el buffer de transmisión Incompleto Condición de Interrupción UTXEx=0 UTXEx=1, Se escribe dato al buffer de transmisión UTXEx=1 Estado de espera (Transmisor Habilitado) Transmisión Deshabilitada Transmisión Activa Character Transmitido UTXEx=0 UTXEx=1 UTXEx=0 y última entrada del buffer es transmitida UxTCTL, Usart Transmit Control Register Habilitación de transmision Habilitación de Transmisión (Transmit Enable)

Habilitación de transmision Habilitación de Transmisión (Transmit Enable) Para transmitir al buffer UTxEX=1 y UTxIFGX=1 El bit TxEPT=1 indica que la transmisión activa se ha completado, esto evita errores

Operación Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de transmisión Generación de la tasa de transferencia Generación de tasa de transferencia Interrupciones

Factor guardado en registros UxBR0 y UxBR1 UxBR0 y UxBR0 , Baud Rate Control Register Generación de la tasa de transferencia (Baude rate) Generacion de la tasa La tasa máxima=1/3 BRCKL Puede generar frecuencias no estándares Baude rate=BRCLK/N

Operación Inicialización y reinicio (reset) Formato del Character Protocolos de comunicación Detección automática de errores Habilitación de recepción Habilitación de transmisión Generación de tasa de transferencia Interrupciones Interrupciones

Interrupciones Interrupciones Vector de interrupciones para transmisión Cuando el buffer está listo UTxIFGX=1 Cuando ya ha transmitido se resetea Vector de interrupciones para recepción URxIFGX=1 Cuando un carácter es recibido y cargado en el buffer Se resetea cuando ha sido leído o la interrupción ha sido servida

UTXIFGX, flag de transmisión URXIFGX, flag de recepción Interrupciones Interrupciones Registros de interrupción 1 y 2

Ejemplo de programación Ejemplo de Programación #include <msp430x14x.h> #include "MSP430lib.c" #include "TRcircbuf.c" void main (void){ /* Inicialización de osciladores (MSP430lib)*/ InitOsc (); /* Inicialización de puertos Entrada/Salida (MSP430lib) */ InitPorts (); /* Inicialización de UART (TRcircbuf) */ RS232Init (); /* Inicialización de LCD (MSP430lib) */ InitLCD ();

Ejemplo de programación(2) Ejemplo de programación /* Loop de recepción*/ while (1){ /* Espera la llegada de un byte a la entada serial y lo almacena en el buffer*/ /* Este estado es interrumpido por RXInterrupt */ if ( RS232RXBufferCount() ){ /* Lee el caracter del buffer y lo almacena en una variable */ RxB = cRS232GetChar(); /* Prende el led */ STATUS_LED_ON;

Ejemplo de programación(3) Ejemplo de programación /* Limpia el LCD */ if (cntr == 0){ SEND_CMD(CLR_DISP); SEND_CMD(DD_RAM_ADDR); } /* Envia el caracter recibido al LCD */ SEND_CHAR(RxB); if(cntr == 15) SEND_CMD(DD_RAM_ADDR2); if(cntr++ == 31) cntr = 0; STATUS_LED_OFF; } } }

RS232RXBufferCount unsigned char RS232RXBufferCount (void) { return (RXCharCount); }

RS232Init void RS232Init (void) { RXWriteIndex = RXReadIndex = RXCharCount = 0; TXWriteIndex = TXReadIndex = TXCharCount = 0; TXBufferEmpty = BUFFER_EMPTY; // reset empty flag InitUART0(); }

cRS232GetChar char cRS232GetChar (void) { char Byte; if (RXCharCount){ /*Verifica si hay char aún disponible */ Byte = RXBuffer[RXReadIndex++];/*Obtiene byte del buffer */ RXReadIndex &= RXBUFSIZE-1; /*Indice de buffer circular */ RX_INT_DISABLE; /*Inhabilita interrupción (IE2) */ RXCharCount--; /*Lectura de un char decrementa la cuenta */ RX_INT_ENABLE; /*Hecho, se habilita interrupción(IE2) */ return (Byte); } else return (0); /*si no hay nuevo char */ }

InitPorts void InitPorts(void) { P1SEL = 0; P1OUT = 0; P1DIR = BIT5 | BIT6; /* enable only Relay outputs */ P2SEL = 0; P2OUT = 0; P2DIR = ~BIT0; /* habilita P2.0 es entrada */ P3SEL |= BIT4 | BIT5; /* enable UART0 */ P3DIR |= BIT4; /* enable TXD0 as output */ P3DIR &= ~BIT5; /* enable RXD0 as input */ P4SEL = 0; P4OUT = 0; P4DIR = BIT2 | BIT3; /* only buzzer pins are outputs */ P6SEL = 0x80; P6OUT = 0; P6DIR = 0x00; /* all output */ }

InitUART0 InitUART0 void InitUART0 (void) /* Inicialización UART0 */ { BCSCTL1 &= ~DIVA0; BCSCTL1 |= DIVA1; /* ACLK = XT1 / 4 */ UCTL0 = CHAR; /* 8 data bits, sin paridad,1 bit de detencion*/ UTCTL0 = SSEL0; /* se elige ACLK como relojpara UART */ U0BR0 = 0xd0; /* 2000000:9600=208 U0BR1 = 0x00; UMCTL0 = 0x00; /* sin modulación*/ ME1 |= UTXE0 | URXE0; /* habilitan modulos de tx y rx UART */ P3SEL |= 0x30; /*define bits de tx y rx P3.4 P3.5 */ P3DIR |= BIT4; /* habilita TXD0 como salida*/ P3DIR &= ~BIT5; /* habilita RXD0 como entrada*/ IE1 |= URXIE0; /*habilita USART0 RX interrupcion*/ IE1 |= UTXIE0; /*habilita USART0 TX interrupcion*/ _EINT(); /* habilita interrupción*/ }

UxTCTL UxCTL Registro de control de tx

uxbr0 Registro de control de tasa de transferencia