Operating System I/O Processes and Device Control

E N D

Presentation Transcript

Processor-memory bus Memory Processor Bus Adapter I/O Device I/O Device Expansion bus I/O Device I/O Bus Bus Adapter I/O Device I/O Device

The Operating System ( OS) controls I/O processes • OS contains the low level programs that control the • I/O device. ( Device Drivers, usually provided by • the device manufacturer)

The Operating System ( OS) controls I/O processes • OS contains the low level programs that control the • I/O device. ( Device Drivers, usually provided by • the device manufacturer) • Limits access to Users for Protection and Resource • Scheduling. ( Some programs violate this)

The Operating System ( OS) controls I/O processes • Contains the low level programs that control the • I/O device. ( Device Drivers, usually provided by • the device manufacturer) • Limits access to Users for Protection and Resource • Scheduling. ( Some programs violate this) • OS must give commands to devices and reads • status from Devices

The Operating System ( OS) controls I/O processes • Contains the low level programs that control the • I/O device. ( Device Drivers, usually provided by • the device manufacturer) • Limits access to Users for Protection and Resource • Scheduling. ( Some programs violate this) • OS must give commands to devices and read • status from Devices • 4. Devices must notify the OS of changes

The Operating System ( OS) controls I/O processes • Contains the low level programs that control the • I/O device. ( Device Drivers, usually provided by • the device manufacturer) • Limits access to Users for Protection and Resource • Scheduling. ( Some programs violate this) • OS must give commands to devices and read • status from Devices • 4. Devices must notify the OS of changes • 5. Data must be transferred between memory and • an I/O device

OS must give commands to devices and read • status from Devices • Special I/O instructions • Store Register xx in Device Address yy

OS must give commands to devices and read • status from Devices • Special I/O instructions • Store Register xx in Device Address yy • Device address is put on I/O control lines and • the data is put on the I/O data lines

OS must give commands to devices and read • status from Devices • Special I/O instructions • Store Register xx in Device Address yy • Device address is put on I/O control lines and • the data is put on the I/O data lines • Write from Device Address yy to a Register • or Memory location

OS must give commands to devices and read • status from Devices • Special I/O instructions • Store Register xx in Device Address yy • Device address is put on I/O control lines and • the data is put on the I/O data lines • Write from Device Address yy to a Register • or Memory location • Constraining for unknown devices

OS must give commands to devices and read • status from Devices • Special I/O instructions • Memory Mapped I/O • Memory Address Space is assigned to Devices.

OS must give commands to devices and read • status from Devices • Special I/O instructions • Memory Mapped I/O • Memory Address Space is assigned to Devices. • A Write to that address goes to a device controller • register and not to the memory ( Commands)

OS must give commands to devices and read • status from Devices • Special I/O instructions • Memory Mapped I/O • Memory Address Space is assigned to Devices. • A Write to that address goes to a device controller • register and not to the memory ( Commands) • A Read of that address comes from a device • controller register and not the memory ( Status)

OS must give commands to devices and read • status from Devices • Special I/O instructions • Memory Mapped I/O • Memory Address Space is assigned to Devices. • A Write to that address goes to a device controller • register and not to the memory ( Commands) • A Read of that address comes from a device • controller register and not the memory ( Status) • Memory Map defined by software for the installed • I/O controllers ( Flexibility and Expandability)

Devices must notify the OS of changes • Polling • Processor periodically reads the status of the I/O • Ex: key depressed, print complete, buffer full

Devices must notify the OS of changes • Polling • Processor periodically reads the status of the I/O • Ex: key depressed, print complete, buffer full • Processor is in complete control

Devices must notify the OS of changes • Polling • Processor periodically reads the status of the I/O • Ex: key depressed, print complete, buffer full • Processor is in complete control • Polling loop in OS is overhead

Devices must notify the OS of changes • Polling • Processor periodically reads the status of the I/O • Ex: key depressed, print complete, buffer full • Processor is in complete control • Polling loop in OS is overhead • Effective on slow devices that initiate I/O • Ex: keyboard and Mouse

Devices must notify the OS of changes • Polling • Processor periodically reads the status of the I/O • Ex: key depressed, print complete, buffer full • Processor is in complete control • Polling loop in OS is overhead • Effective on slow devices that initiate I/O • Ex: keyboard and Mouse

Devices must notify the OS of changes • Polling • Processor periodically reads the status of the I/O • Ex: key depressed, print complete, buffer full • Processor is in complete control • Polling loop in OS is overhead • Effective on slow devices that initiate I/O • Ex: keyboard and Mouse • Not efficient for fast devices

Devices must notify the OS of changes • Polling • Interrupt-driven • Device controller asserts interrupt signal line and • loads interrupt status register.

Devices must notify the OS of changes • Polling • Interrupt-driven • Device controller asserts interrupt signal line and • loads interrupt status register. • Processor checks for interrupt at the start of • each new instruction ( in parallel)

Devices must notify the OS of changes • Polling • Interrupt-driven • Device controller asserts interrupt signal line and • loads interrupt status register. • Processor checks for interrupt at the start of • each new instruction ( in parallel) • Processor recognizes interrupts on a priority basis

Devices must notify the OS of changes • Polling • Interrupt-driven • Device controller asserts interrupt signal line and • loads interrupt status register. • Processor checks for interrupt at the start of • each new instruction ( in parallel) • Processor recognizes interrupts on a priority basis • OS services the interrupt based on the Cause • register or vectored interrupt

Devices must notify the OS of changes • Polling • Interrupt-driven • Device controller asserts interrupt signal line and • loads interrupt status register. • Processor checks for interrupt at the start of • each new instruction ( in parallel) • Processor recognizes interrupts on a priority basis • OS services the interrupt based on the Cause • register or vectored interrupt • Enables a device to signal that data is ready to be • transferred or an operation has been completed

The Operating System ( OS) controls I/O processes • Contains the low level programs that control the • I/O device. ( Device Drivers, usually provided by • the device manufacturer) • Limits access to Users for Protection and Resource • Scheduling. ( Some programs violate this) • OS must give commands to devices and read • status from Devices • 4. Devices must notify the OS of changes • 5. Data must be transferred between memory and • an I/O device

Data must be transferred between memory and an I/O device • Processor Control • Data and Status transferred by Special Instruction • or Memory Mapped I/O

Data must be transferred between memory and an I/O device • Processor Control • Data and Status transferred by Special Instruction • or Memory Mapped I/O • Polling or Interrupts are used

Data must be transferred between memory and an I/O device • Processor Control • Data and Status transferred by Special Instruction • or Memory Mapped I/O • Polling or Interrupts are used • Fast device with blocks of data can excessively • load processor • Ex: hard disk and display

Data must be transferred between memory and an I/O device • Processor Control • Direct Memory Access ( DMA) • I/O controller transfers block of data between device • and memory independent of the processor

Data must be transferred between memory and an I/O device • Processor Control • Direct Memory Access ( DMA) • I/O controller transfers block of data between device • and memory independent of the processor • DMA transfer process • Processor initiates the device operation ( memory • address, number of bytes, enable bus master)

Data must be transferred between memory and an I/O device • Processor Control • Direct Memory Access ( DMA) • I/O controller transfers block of data between device • and memory independent of the processor • DMA transfer process • Processor initiates the device operation ( memory • address, number of bytes, enable bus master) • DMA controller directly transfers block of data • between memory and device, under arbitration

Data must be transferred between memory and an I/O device • Processor Control • Direct Memory Access ( DMA) • I/O controller transfers block of data between device • and memory independent of the processor • DMA transfer process • Processor initiates the device operation ( memory • address, number of bytes, enable bus master) • DMA controller directly transfers block of data • between memory and device, under arbitration • DMA sends interrupt to notify completion or error

Data must be transferred between memory and an I/O device • Processor Control • Direct Memory Access ( DMA) • I/O controller transfers block of data between device • and memory independent of the processor • DMA transfer process • Processor initiates the device operation ( memory • address, number of bytes, enable bus master) • DMA controller directly transfers block of data • between memory and device, under arbitration • DMA sends interrupt to notify completion or error • Enables the processor to continue to operate during • data transfer

I/O bus Control CPU/ Memory Data I/O 1 I/O 2 I/O 3 A bus master controls access to the bus

I/O bus Control CPU/ Memory Data I/O 1 I/O 2 I/O 3 • A bus master controls access to the bus • Slaves request bus access

I/O bus Control CPU/ Memory Data I/O 1 I/O 2 I/O 3 • A bus master controls access to the bus • Slaves request bus access • The bus master generates controls to make the • transfer

I/O bus Control CPU/ Memory Data I/O 1 I/O 2 I/O 3 • A bus master controls access to the bus • Slaves request bus access • The bus master generates controls to make the • transfer • The processor is always a bus master and memory • is always a slave

Typically want multiple bus masters, so need to decide which bus master gets control.

Typically want multiple bus masters, so need to decide • which bus master gets control. • Bus Arbitration • Arbitration schemes are used to grant the bus based on: • Priority • Avoid lockout ( fairness)

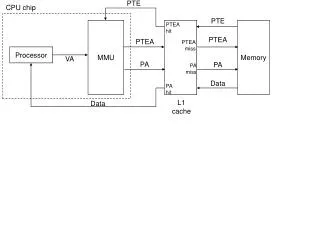

I/O and Caches • Polling or Interrupt- driven I/O under processor • control goes through cache ( virtual and performance)

I/O and Caches • Polling or Interrupt- driven I/O under processor • control goes through cache ( virtual and performance) • DMA goes direct to main memory • Cache coherency problem • ( Cache and memory different) • Cache flushing with hardware support

I/O and Caches • Polling or Interrupt- driven I/O under processor • control goes through cache ( virtual and performance) • DMA goes direct to main memory • Cache coherency problem • ( Cache and memory different) • Cache flushing with hardware support • Page boundaries in virtual memory • Stay within page boundaries or use virtual • addresses

MOUSE Y Counter The movement of the Mouse increments or decrements the X and Y counters X counter

MOUSE Y Counter The movement of the Mouse increments or decrements the X and Y counters. If the location of the cursor is updated 20 times per second it appears smooth to a human. X counter

MOUSE Y Counter The movement of the Mouse increments or decrements the X and Y counters. If the location of the cursor is updated 20 times per second it appears smooth to a human. X counter GIVEN: • Poll at 40 times per second. • 2. Polling I/O routine takes 800 clock cycles • Each counter is 2 Bytes, Sample is 1 Word • Clock Rate is 500 MHz

MOUSE GIVEN: • Poll at 40 times per second. • 2. Polling I/O routine takes 800 clock cycles • Each counter is 2 Bytes, Sample is 1 Word • Clock Rate is 500 MHz % Processor Usage? Each Polling Cycle is 1/40 sec Number of clock cycles each polling cycle = 500x106 clock cycles/sec * 1/40 sec = 12.5 x 106

MOUSE GIVEN: • Poll at 40 times per second. • 2. Polling I/O routine takes 800 clock cycles • Each counter is 2 Bytes, Sample is 1 Word • Clock Rate is 500 MHz % Processor Usage? Each Polling Cycle is 1/40 sec Number of clock cycles each polling cycle = 500x106 clock cycles/sec * 1/40 sec = 12.5 x 106 % Processor Usage = 800 = 64 x 10-6 = 0.0064 % 12.5 x 106