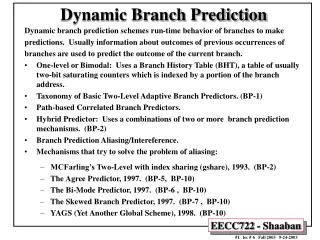

Dynamic Branch Prediction

160 likes | 296 Views

Vincent H. Berk October 18, 2008 Reading for today: 2.1 – 2.5 Reading for Monday: 2.6 – 2.11. Dynamic Branch Prediction. Dynamic Branch Prediction. Control dependences limit ILP Performance = (accuracy, cost of misprediction )

Dynamic Branch Prediction

E N D

Presentation Transcript

ENGS 116 Lecture 9 Vincent H. Berk October 18, 2008 Reading for today: 2.1 – 2.5 Reading for Monday: 2.6 – 2.11 Dynamic Branch Prediction

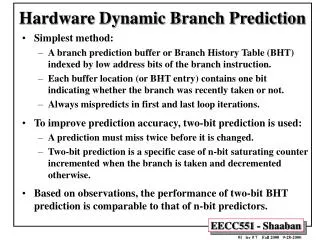

Dynamic Branch Prediction • Control dependences limit ILP • Performance = (accuracy, cost of misprediction) • Branches arrive much faster when multiple instructions are issued per clock • Amdahl’s Law • Want to predict outcome of branch as early as possible • Methods: • Branch history table (1 or more bits) • Correlated branches • Branch target buffer

Dynamic Branch Prediction: A Simple Approach Lower bits of PC T NT T T NT NT . . . • Branch History Table (BHT) (aka Branch Prediction Buffer) • Lower bits of PC address index table of 1-bit values • Entry says whether or not branch taken last time • No address check • Problem: In a loop, 1-bit BHT will cause at least two mispredictions • First time through loop on next time through code, when it predicts exit instead of looping • End of loop case, when it exits instead of looping as before

Taken Taken Predict taken Predict taken Not taken Not taken Taken Not taken Predict not taken Predict not taken Taken Not taken Dynamic Branch Prediction: A Better Way Solution: 2-bit scheme where prediction changes only if we get misprediction twice. Helps when target is known before result of condition.

BHT General Case • n-bit predictor: • counter can hold values between 0 and • predict taken when value is greater than or equal to half of maximum value: • The counter is incremented on each taken branch • and decremented on each not taken branch

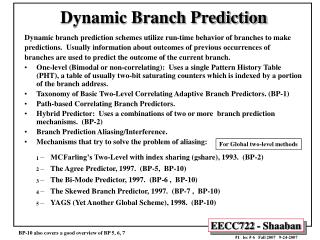

BHT Accuracy • Mispredict because either: • Wrong guess for that branch • Got branch history of wrong branch from index table • 4096-entry table: programs vary from 1% misprediction (nasa7, tomcatv) to 18% (eqntott), with spice at 9% and gcc at 12%. • 4096 entries about as good as infinite number of entries • 2-bit predictors work nearly as well as more-bit predictors

Correlating Branches • Hypothesis: recent branches are correlated; that is, behavior of recently-executed branches affects prediction of current branch • if (d == 0) • d = 1; • if (d == 1) • …

Correlated Branch Prediction • Idea: record m most recently executed branches as taken or not taken, and use that pattern to select the proper n-bit branch history table • In general, (m,n) predictor means record last m branches to select between 2m history tables, each with n-bit counters • Thus, old 2-bit BHT is a (0,2) predictor • Global Branch History: m-bit shift register keeping T/NT status of last m branches. • Each entry in table has mn-bit predictors.

Correlating Branches • (2,2) predictor • – Behavior of recent branches selects between four predictions of next branch, updating just that prediction Branch address 4 2-bits per branch predictor Prediction 2-bit global branch history

Accuracy of Different Schemes(FROM SECOND EDITION) 20% 4096 Entries 2-bit BHT Unlimited Entries 2-bit BHT 1024 Entries (2,2) BHT 18% 16% 14% 12% 11% Frequency of Mispredictions 10% 8% 6% 6% 6% 6% 5% 5% 4% 4% 2% 1% 1% 0% 0% nasa7 matrix300 tomcatv doducd spice fpppp gcc expresso eqntott li 4,096 entries: 2-bits per entry Unlimited entries: 2-bits/entry 1,024 entries (2,2)

Tournament Predictors • Multilevel branch predictor • Use n-bit saturating counter to choose between predictors • Usual choice between global and local predictors

Tournament Predictors: DEC Alpha 21264 • Tournament predictor using 4K 2-bit counters indexed by local branch address. Chooses between: • Global predictor • 4K entries index by history of last 12 branches (212 = 4K) • Each entry is a standard 2-bit predictor • Local predictor • Local history table: 1024 10-bit entries recording last 10 branches, index by branch address • The pattern of the last 10 occurrences of that particular branch used to index table of 1K entries with 3-bit saturating counters

ENGS 116 Lecture 9 Branch target calculation is costly and stalls the instruction fetch. BTB stores PCs the same way as caches The PC of a branch is sent to the BTB When a match is found the corresponding Predicted PC is returned If the branch was predicted taken, instruction fetch continues at the returned predicted PC Branch Target Buffers

ENGS 116 Lecture 9 Branch Target Buffers

ENGS 116 Lecture 9 Enter branch instruction PC and next PC into branch target buffer Figure 3.20 The steps involved in handling an instruction with a branch-target buffer Send PC to memory and branch-target buffer IF No Yes Entry found in branch-target buffer? Send out predicted PC No Yes Is instruction ataken branch? ID No Yes Normal instruction execution Branch taken? Mispredicted branch, kill fetched instruction; restart fetch at other target; delete entry from target buffer Branch correctly predicted; continue execution with no stalls EX