CIRCUITE NUMERICE

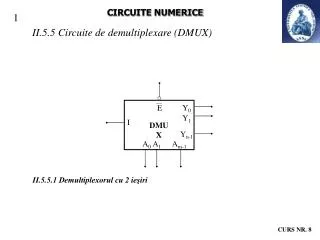

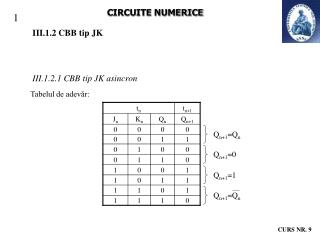

Y 0. E. Y 1. I. DMUX. Y n-1. A 0. A 1. A m-1. CIRCUITE NUMERICE. 1. II.5. 5 Circuite de de multiplexare ( D MUX). II.5.5.1 Demultiplexorul cu 2 ieşiri. CURS NR. 8. A. I. Y 0. Y 1. Y 0. DMUX 1:2. I. Y 1. 0. 0. 0. 0. I. A. A I. A I. 0. 0. 1. 1. Y 0 =I.

CIRCUITE NUMERICE

E N D

Presentation Transcript

Y0 E Y1 I DMUX Yn-1 A0 A1 Am-1 CIRCUITE NUMERICE 1 II.5.5 Circuite de demultiplexare (DMUX) II.5.5.1 Demultiplexorul cu 2 ieşiri CURS NR. 8

A I Y0 Y1 Y0 DMUX 1:2 I Y1 0 0 0 0 I A A I A I 0 0 1 1 Y0=I 0 1 1 0 0 0 0 0 0 0 1 0 0 0 1 1 1 0 0 1 Y1=I 1 1 0 1 A·I I A = · Y1 I A = · Y0 A CIRCUITE NUMERICE 2 Astfel tabelul de adevăr al circuitului arată astfel: diagramele VK sunt: A·I Y1= Y0= Conform cu ecuaţiile găsite schema logică a circuitului va fi: CURS NR. 8

0 0 0 0 0 0 0 Y0=I 0 0 1 1 0 0 0 0 1 0 0 0 0 0 Y1=I 0 1 1 0 1 0 0 1 0 0 0 0 0 0 Y0 Y2=I 1 0 1 0 0 1 0 Y1 DMUX 1:4 I 1 1 0 0 0 0 0 Y3=I Y2 1 1 1 0 0 0 1 A0 A1 Y3 A1 A0 I Y0 Y1 Y2 Y3 CIRCUITE NUMERICE 3 II.5.5.2 Demultiplexorul cu 4 ieşiri Tabelul de adevăr: CURS NR. 8

I Y0 A1A0 I A1A0 I A1A0 I A1A0 I 00 00 00 00 01 01 01 01 11 11 11 11 10 10 10 10 Y1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Y2 I·A1·A0 I·A1·A0 I·A1·A0 1 1 1 1 0 0 0 1 0 1 0 0 0 0 1 0 0 0 1 0 Y3 Y0a Y1a Y2a Y3a Y0b Y1b Y2b Y3b Y0 Y1 Y2 Y15 Ea Eb SN74155 E0 SN74154 Ea Eb E1 A0 A1 A B C D demultiplexor 1:16 demultiplexor dublu 1:4 A0 A1 CIRCUITE NUMERICE 4 Y0 = Y1 = Y2 = Y3 = I·A1·A0 CURS NR. 8

Y0 Y0 Y1 Y1 Y2 Y2 Y3 Y3 Y4 Y4 Y5 Y5 Y6 Y6 Y7 Y7 A0 A0 A1 A1 A2 A2 E Y0 Y1 Y2 Y3 Y15 Y0 Y1 Y2 Y3 Y15 E0 SN74154 E1 A B C D A B C D Y0 Y0 Y1 Y1 Y2 Y2 Y3 Y3 Y4 Y4 Y5 Y5 Y6 Y6 Y7 Y7 Y8 Y8 Y9 Y9 SN7442 SN7442 A A B B C C D D CIRCUITE NUMERICE 5 I I a) demultiplexor realizat cu un decodificator b) demultiplexor realizat cu un decodificator c) decodificator realizat cu un demultiplexor CURS NR. 8

Y240 Y0 Y1 Y2 Y16 Y17 Y15 Y31 Y241 Y243 Y255 Y18 A0 A1 A2 A3 Y0 Y0 Y0 Y0 Y1 Y1 Y1 Y1 Y2 Y2 Y2 Y2 Y15 Y15 Y15 Y15 E0 E0 E0 E0 SN74154 SN74154 SN74154 SN74154 E1 E1 E1 E1 A A A A B B B B C C C C D D D D A4 A5 A6 A7 I E CIRCUITE NUMERICE 6 II.5.5.3 Extinderea capacităţii demultiplexoarelor CURS NR. 8

A>B A>B A n Comparator numeric A=B A=B B n A<B A<B A CN 1 bit B CIRCUITE NUMERICE 7 II.5.6. Comparatoare numerice II.5.6.1 Comparatorul numeric de 1 bit CURS NR. 8

A B YA<B YA=B YA>B 0 0 0 1 0 A<B A>B A=B A=B 0 1 1 0 0 A B A B A B 0 0 0 1 1 1 1 1 1 0 0 0 0 1 0 1 0 0 0 0 0 1 1 0 0 1 1 1 0 1 0 0 1 0 B·A A·B = AB A·B YA<B A YA=B B YA>B CIRCUITE NUMERICE 8 Tabelul de adevăr al comparatorului de 1 bit: YA<B= + A·B YA=B= YA>B= CURS NR. 8

YA>B=1 YA>B=1 > > A0 A1 B1 B0 YA1=B1=1 YA=B=1 YA>B, YA=B, YA<B=0 = = < < YA<B=1 YA<B=1 CIRCUITE NUMERICE 9 II.5.6.2 Comparatorul numeric de 2 biţi A=A1·21+ A0·20 B=B1·21+ B0·20 CURS NR. 8

YA1<B1 YA<B CN 1bit YA1=B1 Logică de decizie YA1>B1 YA=B YA0<B0 A1 CN 1bit B1 YA0=B0 A0 B0 YA>B YA0>B0 CIRCUITE NUMERICE 10 Observaţii: Conform cu observaţiile de mai sus putem realiza schema comparatorului de 2 biţi: CURS NR. 8

A03 A47 A B03 B47 B A0 A0 A0 A1 A1 A1 A2 A2 A2 A3 A3 A3 B0 B0 B0 B1 B1 B1 B2 B2 B2 B3 B3 B3 IA>B IA>B IA>B OA>B OA>B OA>B SN7485 SN7485 SN7485 IA=B IA=B IA=B OA=B OA=B OA=B IA<B IA<B IA<B OA<B OA<B OA<B GND către etajele următoare VCC GND CIRCUITE NUMERICE 11 Există circuite integrate comparatoare de 4 biţi, SN7485: II.5.6.3 Expandarea comparatoarelor CURS NR. 8

x0 y0 x0 y0 0 0 1 1 0 0 0 0 1 0 1 1 1 0 1 0 x0 y0 s0 t1 x0·y0 + x0·y0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 CIRCUITE NUMERICE 12 II.5.7. Sumatoare numerice II.5.7.1 Semisumatorul elementar Tabelul de adevăr al circuitului: s0= suma pentru rangul 0 t1= transportul către rangul 1 Diagramele VK: = x0y0 x0·y0 t1= s0= CURS NR. 8

t1 x0 s0 y0 CIRCUITE NUMERICE 13 Schema semisumatorului arată ca în figură: II.5.7.2 Sumatorul elementar CURS NR. 8

1 1 0 1 1 0 0 0 1 0 0 1 1 1 0 0 1 1 0 1 0 0 1 0 0 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 xk yk tk-1 sk tk+1 sk xk xkyk tk-1 xkyk tk-1 00 00 01 01 11 11 10 10 tk+1 k yk 0 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 0 1 tk-1 xk·yk·tk-1 + xk·yk·tk-1 (xk·yk+ xk·yk)·tk-1 + xk·yk·tk-1 + xk·yk·tk-1 xk·yk·tk-1 xk·(yk·tk-1+ yk·tk-1) + xk·(yk·tk-1+ yk·tk-1) xk·(yktk-1) + xk·(yktk-1) CIRCUITE NUMERICE 14 Tabelul de adevăr: Diagramele VK: + xk·yk·tk-1 = sk = tk+1 = + xk·yk = = = + xk·yk = = (xkyk)·tk-1 = + xk·yk = xk yk tk-1 = CURS NR. 8

xk sk yk tk+1 tk-1 x0 y0 x1 y1 xn-1 yn-1 xk xk xk yk yk yk tk-1 tk-1 tk-1 k k k tk+1 tk+1 tk+1 sk sk sk s0 s1 sn-1 sn CIRCUITE NUMERICE 15 II.5.7.3 Expandarea sumatoarelor . . . GND CURS NR. 8