µP - 68000

60 likes | 227 Views

µP - 68000. David Saint-Mellion. Organisation interne. Processeur 32 bits en interne : 8 registres de Données D7 -D0 de 32 bits. Adressage sur 24 bits (16 Mo). Registres Adresses 32 bits. PC : Compteur Programme, pointe sur l’adresse de l ’instruction suivante.

µP - 68000

E N D

Presentation Transcript

µP - 68000 David Saint-Mellion

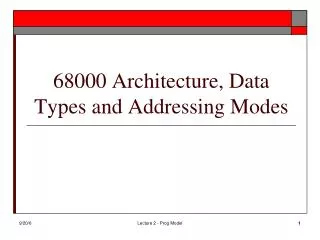

Organisation interne Processeur 32 bits en interne : 8 registres de Données D7 -D0 de 32 bits Adressage sur 24 bits (16 Mo). Registres Adresses 32 bits PC : Compteur Programme, pointe sur l’adresse de l ’instruction suivante. USP - SSP - A7 : pointeurs de pile. A7 contient le pointeur de pile de l ’état courant A0 - A6 : 7 registres adresses banalisés

µ P 68000 / UDS / LDS D15 -D8 D7 -D0 A23 - A1 8 8 23 MémoireHaute @ paire MémoireBasse @ impaire Transfert - bus Adresses-Données Bus Données de 16 lignes D15 - D0. Transfert en 2 passes des objets de 32 bits. Alignement Gros Boutiste.L’octet bas stocké à une adresse impaire.Ne supporte que le mode aligné - IT « Erreur d ’adresse » /UDS et /LDS informations de validation busDonnées Haut et Bus Données Bas. Bus Adresses 23 lignes A23 - A1. La ligne A0 non distribuée.

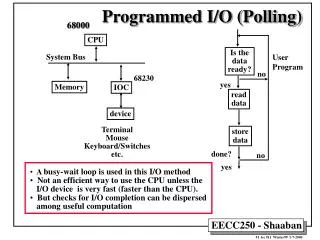

R/W /AS=0 /DTACK=0 /AS µP Composant t /DTACK t Protocole Principe Le protocole est asynchrone avec poignée de main • Le µP marque le début de l ’échange en validant /AS Poignée de Main • Le composant signale qu’il s’est acquitté des Données en validant /DTACK • R/W sens de transfertR/W = «1» lectureR/W = «0» écriture La poignée de main : • /AS - Address Strobe • /DTACK Data Transfer Acknowledge

/AS=0 Chien deGarde /BERR µP Composant cycle bus trop longue/BERR =0IT « Bus Erreur /AS t Chien de garde activé Chien de garde activé Chien de garde activé Protocole - Chien de garde Le protocole peut être bloquant si le composant ne valide pas /DTACK. Un chien de garde surveille la durée du cycle bus. Il est actif lorsque /AS=0 Si le temps du cycle est trop long, le chien de garde active la borne /BERR du µP qui produit l’IT « Erreur de Bus ».

µP 68000 Table des vecteurs PC 4 - @ 1ère instruction SSP 0 - pointeur de Pile /HALT /RESET µP 68000 t T > 100ms /HALT /RESET Le Reset - Initialisation du µP Au Reset, le µp prélève dans la table des vecteurs : • La valeur du pointeur de pile superviseur à l’@ «0» • La valeur de l’adresse de la 1ère instruction à l’@ «4» Le Reset se produit lorsque /HALT et /RESET passent à «1» après un temps mini de 100 ms à «0» L’information /HALT et /RESET est élaborée à partir de la présence de l ’alimentation ou de l’état d ’un B.P. RAZ