GTS /SEGMENT

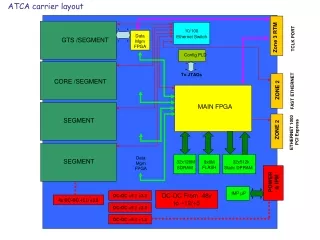

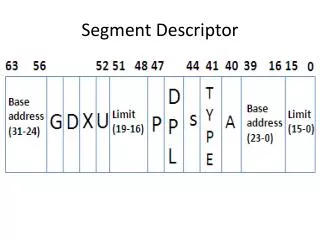

ATCA carrier layout. 10/100 Ethernet Switch. Data Mgm FPGA. Zone 3 RTM. TCLK PORT. GTS /SEGMENT. Config PLD. To JTAGs. CORE /SEGMENT. ZONE 2. FAST ETHERNET. MAIN FPGA. SEGMENT. ZONE 2. ETHERNET 1000 PCI Express. Data Mgm FPGA. 32x128M SDRAM. 32x512k Static DPRAM.

GTS /SEGMENT

E N D

Presentation Transcript

ATCA carrier layout 10/100 Ethernet Switch Data Mgm FPGA Zone 3 RTM TCLK PORT GTS /SEGMENT Config PLD To JTAGs CORE /SEGMENT ZONE 2 FAST ETHERNET MAIN FPGA SEGMENT ZONE 2 ETHERNET 1000 PCI Express Data Mgm FPGA 32x128M SDRAM 32x512k Static DPRAM SEGMENT 8x8M FLASH POWER & IPM IMP µP DC-DC From -48v to +12/+5 DC-DC +5 +3.3 4x DC-DC +5 +3.3 DC-DC +5 +2.5 DC-DC +5 +1.2

200Mhz Clock distribution tpd1 , skew1, jitter1 GTS_CLOCK TCLK PORT GTS FANOUT 1:2 2 1 tpd2 , skew2, jitter2 Jitter 10ps Jitter 14ps DELAY LINE SYNC CORE tpd4 , skew4, jitter4 tpd3 , skew3, jitter3 SYNC_RTN FANOUT 1:6 SWITCH SEGMENT 4 tpd5 , skew5, jitter5 Jitter 10ps MAIN FPGA SMB INSP SEGMENT TCLK PORT SEGMENT FANOUT 1:2 DELAY LINE SYNC SEGMENT 5 SYNC_RTN FANOUT 1:6 SWITCH tpd Master = tpd1+tpd2+tpd3+tpd4 tpd Slave = tpd1+tpd5+tpd3+tpd4 skew Master = skew1+skew2+skew3+skew4 skew Slave = skew1+skew5+skew3+skew4 jitter Master2 = jitter_clock2+jitter12+jitter22+jitter32+jitter42 jitter Master2 = jitter_clock2+jitter52+jitter22+jitter32+jitter42 SEGMENT 6 3 MAIN FPGA SMB INSP SEGMENT

Bcast & Msg Handler 1/2 FROM REMOTE (TCLK) 8 B_cast_data (7 downto 0) B_cast_str0 FANOUT TO MAIN FPGA, LOCALS MEZZANINES, AND REMOTE MEZZANINES (TCLK) SERIALIZERS 81 8 B_cast_str1 TRG/BCT FPGA 8 GTS Status (7 downto 0) GTS MEZZANINE MAIN FPGA LLP Status (7 downto 0) Msg_data (7 downto 0) Msg_str0 Msg_str1 FROM REMOTE (TCLK) Concentrator SEG/CORE MEZZANINE 8 LLP Status (7 downto 0) SERIALIZERS 81 TO REMOTE (TCLK) 8 Msg_data (7 downto 0) Msg_str0 8 Msg_str1

Bcast & Msg Handler 1/2 TCLK PORT GTS Serializers FPGA CORE SEGMENT MAIN FPGA SEGMENT TCLK PORT SEGMENT Serializers FPGA SEGMENT SEGMENT MAIN FPGA SEGMENT

TRIGGER Handler 1/2 Trig_val (1 downto 0) 8 Trig_Rej (1 downto 0) FANOUT TO OTHERS DEST Lt_data (7 downto 0) 8 SERs / DESERs 81 Lt_Strobe 8 GTS MEZZANINE Tv_data (7 downto 0) Tv_Strobe Trig_req (1 downto 0) MAIN FPGA Trig_req (1 downto 0) CORE MEZZANINE

TRIGGER Handler 2/2 TCLK PORT GTS Serializers FPGA CORE SEGMENT MAIN FPGA SEGMENT TCLK PORT SEGMENT Serializers FPGA SEGMENT SEGMENT MAIN FPGA SEGMENT

Data readout engine Using 1 16 bit port : 128 words/event 256 bytes/event 6 channels 1536bytes 16bit bus @ 100MHz Need 7.68µs (20µs avaible @ 50KHz) 1536*4 = 6144 byte/Event 32bit bus @ 100MHz Need 15.36µs (20µs avaible @ 50KHz) 8 pairs ; 16 I/O Serializer Data_A (15 downto 0) Deserializer Serializer Serializer Empty_A Serializer 32bit Data_Ready_A 32bit 1024x18 DPRAM Data_Request_A Data_A (15 downto 0) 9bit 9bit Empty_A Data_Ready_A Data_Request_A 1024x18 DPRAM X4 Mezzanines

MGT Clocking Layout RocketIO 101 MUX USER SMA MGTclk M34/N34 RocketIO 102 ATCA FABRIC CHANNEL6 INSPECTION PADS MUX 200MHz GTS Clock ATCA FABRIC CHANNEL5 MGTclk AP28/AP29 RocketIO 103 ATCA FABRIC CHANNEL4 MUX ATCA FABRIC CHANNEL3 RocketIO 105 ATCA FABRIC CHANNEL2 MUX ATCA FABRIC CHANNEL1 (**) The ATCA FABRIC channels are routed from CHANNEL1 to CHANNEL12 by switches 200MHz to 250MHz PLL RocketIO 106 MUX EPSON 250MHz RocketIO 109 MUX MGTclk AP3/AP4 RocketIO 110 MUX MGTclk J1/K1 RocketIO 112 RTM PCI EXPRESS LANE3 MUX RTM PCI EXPRESS LANE2 PCI Express JITTER ATTENUATOR FROM SFP TRANSCEIVER RocketIO 113 RTM PCI EXPRESS LANE1 FROM RTM MUX RTM PCI EXPRESS LANE0 INSPECTION PADS RocketIO 114 MUX USER SFP TRANSCEIVER (***) User SFP could be used as 1GEnet or PCIExpress DAQ without FABRIC

MGT Layout MGT112A RocketIO ZONE3 (RTM) PCI Express Lane 0 MGT112B RocketIO ZONE3 (RTM) PCI Express Lane 1 MGT113A ZONE3 (RTM) PCI Express Lane 2 RocketIO MGT113B ZONE3 (RTM) PCI Express Lane 3 RocketIO MGT114A RocketIO iSFP Cage (1GEthernet,PCI Espress,User …) (*) Clock in Cage To clock management (*) RocketIO FABRIC CHANNEL12 MGT102A TEST FABRIC CHANNEL11 FABRIC CHANNEL10 RocketIO MGT102B FABRIC CHANNELL9 TEST RocketIO FABRIC CHANNELL8 MGT103A FABRIC CHANNELL7 TEST The ATCA FABRIC is a DUAL STAR. This means that CHANNELS 1 of slot from 3 to 14 are are routed on CHANNEL1 to CHANNEL12 on HUB1 and CHANNELS 2 of slot from 3 to 14 are are routed on CHANNEL1 to CHANNEL12 on HUB2 FABRIC CHANNELL6 RocketIO MGT103B FABRIC CHANNELL5 TEST RocketIO FABRIC CHANNELL4 MGT105A FABRIC CHANNELL3 TEST FABRIC CHANNELL2 RocketIO (*) MGT105B (*) These cnannel must be routed on LLP cards, the others Channels are needed only on central switch. FABRIC CHANNELL1 (*) TEST

AC VIAS N P N P P VIAS AC VIAS N N P AC P VIAS N N AC P N P N P AC AC MGT topology template AC N P N P AC P N N AC P AC P VIAS N N VIAS AC P N P N P AC

PCI Express topology template P AC AC N P VIAS N P VIAS N P VIAS AC AC VIAS N N P N P N P N P P AC AC N P VIAS N P VIAS N P VIAS AC VIAS AC N N P N P N P N P

ATCA Configuration and status TCK0 TMS0 TDI0 TDO0 Xc9500 pld TCK_RTM TMS_RTM TDI_RTM TDO_RTM MEZZANINE0 TCK1 TMS1 TDI1 TDO1 TCK_PPC TMS_PPC TDI_PPC TDO_PPC MEZZANINE1 RTM/PPC TCK2 TMS2 TDI2 TDO2 MEZZANINE2 CONF[1..0] MEZZANINE 0 CONF[1..0] MEZZANINE 1 CONF[1..0] MEZZANINE 2 TCK3 TMS3 TDI3 TDO3 CONF[1..0] MEZZANINE 3 MEZZANINE3 FPGA_INIT/PROGRAM MEZZANINE 0 FPGA_INIT/PROGRAM MEZZANINE 1 TCK4 TMS4 TDI4 TDO4 FPGA_INIT/PROGRAM MEZZANINE 2 MAIN FPGA FPGA_INIT/PROGRAM MEZZANINE 3 FPGA_INIT/PROGRAM MAIN FPGA FPGA_INIT/PROGRAM TRG FPGA TCK5 TMS5 TDI5 TDO5 FPGA TRIGGER SEL PROGRAM MEZZANINE 0 SEL PROGRAM MEZZANINE 1 SEL PROGRAM MEZZANINE 2 SEL PROGRAM MEZZANINE 3 TCK6 TMS6 TDI6 TDO6 AUX_1 SEL PROGRAM MAIN FPGA SEL PROGRAM TRG FPGA I2C_SCK TCK7 TMS7 TDI7 TDO7 AUX_2 I2C_SCL

ATCA I2C Layout and addressing Mezzanine 1 Address $00 Mezzanine 1 Address $00 Mezzanine 1 Address $00 Mezzanine 1 Address $00 Monitoring ADC Address $00 Serial EEPROM Address $00 Temp Sensor 1 Address $00 Address $00 Temp Sensor 2 Address $00 IPMB1 Temp Sensor 3 Address $00 Address $00 IPMB0 Jtag Supervisor Address $00 SWITCHS Supervisor Address $00 Address $00 Main Fpga

ATCA Power Supply 4x POWER ONE YS12S10 55W DC to DC Converter P3V3-5A 16.5W P3V3/P2V5 Linear Reg P2V5-1.5A VCCAUX Fpga 1 MEZZANINE 1 DC to DC Converter Fusing Filtering Protection Hot Swap P3V3-5A 16.5W MEZZANINE 2 P5V0/P2V5 Linear Reg P2V5-1.5A VCCAUX Fpga 2 -48V DC DC to DC Converter P5V0/P2V5 Linear Reg P2V5-1.5A P3V3-5A 16.5W MEZZANINE 3 VCCAUX MGT DC to DC Converter P5V0/P1V8 Linear Reg P1V8-0.5A P3V3-5A 16.5W MEZZANINE 4 PROMS ENABLE P5V0/P1V2 Linear Reg P1V2-0.5A VTTTXs ATC210 (210W) P12V-14.7A 176.7(160.6)W M48/P12 DC DC P5V0-6A 30W P5V0/P1V2 Linear Reg P1V2-0.5A VTTRXs P12/P5V0 DC DC M48V-4.0A 194.4(176.7)W P3V3_BOOT P3V3-7A 23.1W P12/P3V3 DC DC MAIN BOARD P12/P2V5 DC DC P2V5-7A 17.5W MAIN BOARD P12/P1V2 DC DC P1V2-7A 8.4W FPGAs CORE DC-DC Efficency is estimated at least 90% P12/P1V2 DC DC P1V2-4A 4.8W FPGA MGT P12/P1V8 DC DC P1V8-6A 10.8W MGT BUFFERS 6x POWER ONE YS12S10 55W

8 Data_A (15 downto 0) 8 Empty_A MII port Data_Request_A 8 Data_Ready_A 8 Jtag and config Data_B(15 downto 0) Empty_B Serial_Tx 4 Data_Request_B Serial_Rx Data_Ready_B 2 I2C_Sck Trig_req (1 downto 0) I2C_Sda Trig_val (1 downto 0) Cfg(1downto 0) 16 pairs 32 I/O 2 Trig_Rej (1 downto 0) SER / DESER 81 8 Lt_data (7 downto 0) Lt_Strobe 8 SEGMENT/ CORE MEZZANINE Tv_data (7 downto 0) 6 Tv_Strobe 8 Msg_data (7 downto 0) Msg_str0 Segment / Core mezzanine I/O model 2 Msg_str1 B_cast_data (7 downto 0) 8 B_cast_str0 B_cast_str1 2 SMB INSP LLP Status (7 downto 0) 8 GTS Status (7 downto 0) 8 8 SPARE OUT 6 8 SPARE IN 2 CLOCK

MII port Jtag and config Serial_Tx Serial_Rx I2C_Sck Trig_req (1 downto 0) I2C_Sda Trig_val (1 downto 0) Cfg(1downto 0) 9 pairs 18 I/O 2 Trig_Rej (1 downto 0) SER / DESER 81 8 Lt_data (7 downto 0) Lt_Strobe 8 GTS MEZZANINE Tv_data (7 downto 0) 6 Tv_Strobe 8 Msg_data (7 downto 0) Msg_str0 2 Msg_str1 B_cast_data (7 downto 0) 8 B_cast_str0 GTS mezzanine I/O model B_cast_str1 2 SMB INSP LLP Status (7 downto 0) 8 GTS Status (7 downto 0) 8 8 SPARE OUT 6 8 SPARE IN 2 CLOCK

GTS mezzanine I/O model PREPROC 1 PREPROC 2 PREPROC 3 PREPROC 4 TCLK_RTM MAIN_FPGA Trig_req (1 downto 0) 8 Trig_val (1 downto 0) 8 Trig_Rej (1 downto 0) Lt_data (7 downto 0) 8 Lt_Strobe FANOUT TO OTHERS DEST 8 Tv_data (7 downto 0) Tv_Strobe 8 GTS MEZZANINE SER / DESER 81 8 B_cast_data (7 downto 0) B_cast_str0 B_cast_str1 GTS Status (7 downto 0) 8 8 LLP Status (7 downto 0) 8 Msg_data (7 downto 0) Msg_str0 Msg_str1 SMB INSP FROM TCLK (SLAVE MODE)

GTS CLOCK 1 tpd1 OUT FIRST FANOUT 1:2 2 tpd5 OUT AFTER TCLK PORT 3 tpd4 OUT AFTER FANOUT 1:8 4 Tpd2 OUT AFTER DELAY LINE 5 tpd4 OUT AFTER FANOUT 1:8 6