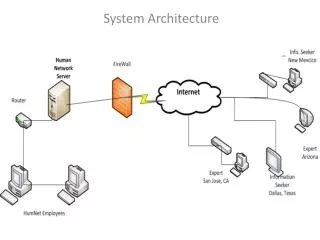

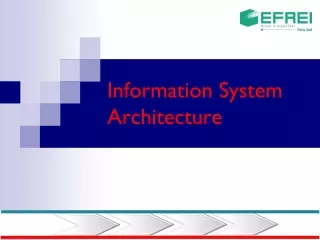

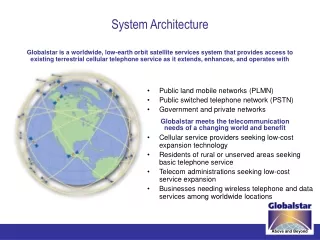

System Architecture

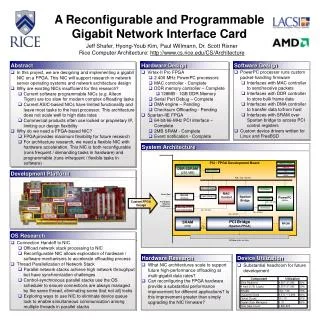

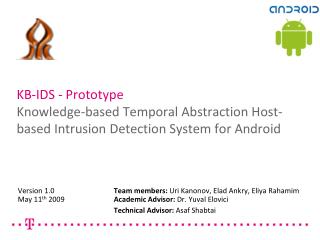

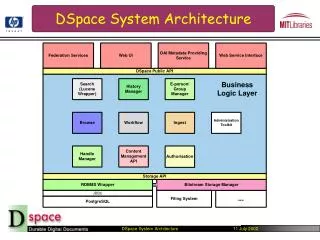

This project focuses on the design and implementation of a reconfigurable gigabit network interface card (NIC) on an FPGA platform, aimed at facilitating research in network operating systems and architecture. It integrates a PowerPC processor running custom firmware, various memory controllers (DDR, SRAM), and full duplex Ethernet capabilities. The architecture addresses the limitations of existing NICs by allowing hardware acceleration and flexibility for experimental and high-performance applications. Key features include interfacing with MAC and DMA controllers, enabling efficient data packet transfers and processing.

System Architecture

E N D

Presentation Transcript

PCI / FPGA Development Board Memory / Control DDR-SDRAM (256 MB) Ethernet Serial Port DDR Controller PCI Debug DDR PLB – 64b / 100 MHz Virtex FPGA PLB / OPB Bridge MAC Control Spartan FPGA Spartan Bridge BRAM Block PowerPC300MHz Serial Port RJ-45 Port RS-232 (Debug) UART (OPB Bus) On-Chip Mem Full Duplex Ethernet 2 GBits/sec 32b / 125 MHz Ethernet PHY PCI Interface Ethernet PHY (10/100/1000) BRAM Block 8b / 125 MHz 32b / 66 MHz 64b / 66 MHz SRAM (2MB) PCI Bridge (Spartan FPGA) PROM 32b /66 MHz PCI Bus (64b / 66 MHz) A Reconfigurable and Programmable Gigabit Network Interface Card Jeff Shafer, Hyong-Youb Kim, Paul Willmann, Dr. Scott RixnerRice Computer Architecture: http://www.cs.rice.edu/CS/Architecture Abstract Hardware Design Software Design • PowerPC processor runs custom packet-handling firmware • Interfaces with MAC controller to send/receive packets • Interfaces with DDR controller to store bulk frame data • Interfaces with DMA controller to transfer data to/from host • Interfaces with SRAM over Spartan bridge to access PCI control registers • Custom device drivers written for Linux and FreeBSD • Virtex-II Pro FPGA • 2 400 MHz PowerPC processors • MAC controller - Complete • DDR memory controller – Complete • 128MB - 1GB DDR Memory • Serial Port Debug – Complete • DMA engine – Pending • Checksum Offloading - Pending • Spartan-IIE FPGA • 64-bit/66-MHz PCI interface – Complete • 2MB SRAM - Complete • Event notification - Complete • In this project, we are designing and implementing a gigabit NIC on a FPGA. This NIC will support research in network server operating systems and network architecture design • Why are existing NICs insufficient for this research? • Current software programmable NICs (e.g. Alteon Tigon) are too slow for modern complex offloading tasks • Current ASIC-based NICs have limited functionality and leave most tasks to the host processor. This architecture does not scale well to high data rates • Commercial products often use locked or proprietary IP, limiting our design flexibility • Why do we need a FPGA-based NIC? • FPGA provides maximum flexibility for future research • For architecture research, we need a flexible NIC with hardware acceleration. This NIC is both reconfigurable (runs frequent / demanding tasks in hardware) and programmable (runs infrequent / flexible tasks in software) System Architecture Development Platform Custom FPGA Design OS Research • Connection Handoff to NIC • Offload network stack processing to NIC • Reconfigurable NIC allows exploration of hardware / software mechanisms to accelerate offloading process • Thread Parallelization of Network Stack • Parallel network stacks achieve high network throughput but have synchronization challenges • Control-synchronous parallel stacks use the OS scheduler to ensure connections are always managed by the same thread, eliminating some (but not all) locks • Exploring ways to use NIC to eliminate device queue lock to enable simultaneous communication among multiple threads in parallel stacks Hardware Research Device Utilization • What NIC architectures scale to support future high-performance offloading at multi-gigabit data rates? • Can reconfiguring the FPGA hardware provide a substantial performance improvement for different applications? Is this improvement greater than simply upgrading the NIC firmware? • Substantial headroom for future development