High-Performance WEP Co-Processor Project

The WEP co-processor project aims to minimize delay and area while selecting the FPGA device, optimizing analysis, synthesis, and routing for achieving set ALUTs and Registers, with specific clock cycles and period. The project strives towards efficient performance within defined metrics.

High-Performance WEP Co-Processor Project

E N D

Presentation Transcript

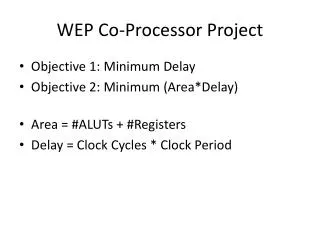

WEP Co-Processor Project • Objective 1: Minimum Delay • Objective 2: Minimum (Area*Delay) • Area = #ALUTs + #Registers • Delay = Clock Cycles * Clock Period

WEP Co-Processor Project • Choose the following FPGA device: • Arria GX • EP1AGX90EF1152I6 • Run the entire compilation process, including: • Analysis and Synthesis • Place and Route • Assembler and Timing Analyzer

This Should be Achievable • Area • #ALUTs = 7634 • #Registers = 2158 • Area = #ALUTs + #Registers = 9792 • Delay • Clock Cycles = 739 cycles • Clock Period = 13.09 ns • Delay = Clock Cycles * Clock Period = 9.67 ms • Area*Delay = 0.094723

Target • Try to get within factor of 2x for Delay and (Area*Delay) • That is, try to achieve • Delay ≤ 19.34 ms • (Area*Delay) ≤ 0.189446