High-Priority Register Output and Auto-Output Testing for HCC Systems

This document details the functionalities of the HCC Test Data Outputs focusing on the high-priority register. The output is automatically generated whenever the register's value changes, facilitating efficient debugging and testing. Upon power-up, the HCC outputs an 8x64bit repeating data block at 40 MHz, which includes a low-priority read packet and a series of balanced bit patterns. The periodic high-priority output can also be configured for programmable intervals, aiding in synchronization and decoding with both scope and FPGA setups for diverse applications.

High-Priority Register Output and Auto-Output Testing for HCC Systems

E N D

Presentation Transcript

High Priority Register Normally sent out (Register Read packet) whenever its value changes. HCC Test Data Outputs

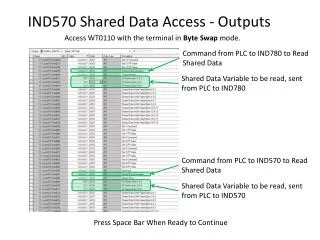

Auto Output To facilitate testing of the HCC, on power up, the HCC will output a repeating 8x64bit data block at 40 MHz: 1x64-bit block: HCC low priority read packet with the contents of the high priority register 7x64-bit blocks: unique sequence of fixed bit patterns that is balanced AND’ed with output of data concentrator HCC Test Data Outputs

Auto Output (2) Makes it possible to determine where you are in the sequence for both scope and FPGA decoding Works for both DC and AC coupling HCC Test Data Outputs

Periodic High Priority Output High Priority Register read packet will be generated whenever HP register value changes A mode can be set that will generate an HP read packet at a programmable interval through the data concentrator Enables easy sync to output, without requiring ABC May be useful for various debugging tasks HCC Test Data Outputs