Chapter 6, Overview

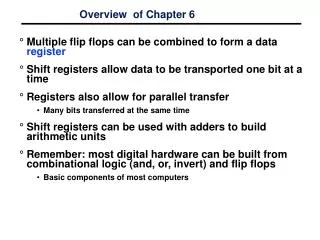

Chapter 6, Overview. Multiple flip flops can be combined to form a data register Shift registers allow data to be transported one bit at a time Registers also allow for parallel transfer Many bits transferred at the same time

Chapter 6, Overview

E N D

Presentation Transcript

Chapter 6, Overview • Multiple flip flops can be combined to form a data register • Shift registers allow data to be transported one bit at a time • Registers also allow for parallel transfer • Many bits transferred at the same time • Shift registers can be used with adders to build arithmetic units • Remember: most digital hardware can be built from combinational logic (and, or, invert) and flip flops • Basic components of most computers

Register with Parallel Load • Register: Group of Flip-Flops • Ex: D Flip-Flops • Holds a Word (Nibble) of Data • Loads in Parallel on ClockTransition • Asynchronous Clear (Reset)

Register with Load Control • Load Control = 1 • New data loadedon next positiveclock edge • Load Control = 0 • Old data reloadedon next positiveclock edge

Shift Registers • Cascade chain of Flip-Flops • Bits travel on Clock edges • Serial in – Serial out, can also have parallel load / read

Parallel Data Transfer • All data transfers on rising clock edge • Data clocked into register Y

Parallel versus Serial • Serial communications is defined as • Provides a binary number as a sequence of binary digits, one after another, through one data line. • Parallel communications • Provides a binary number through multiple data lines at the same time.

Shift register application • Parallel-to-serial conversion for serial transmission parallel outputs parallel inputs serial transmission

Serial Transfer • Data transfer one bit at a time • Data loopback for register A Time T0 T1 T2 T3 T4 Reg A 1011 1101 1110 0111 1011 Reg B 0011 1001 1100 0110 1011

Serial Transfer of Data • Transfer from register X to register Y (negative clock edges for this example)

OUT OUT1 OUT2 OUT3 OUT4 D Q D Q D Q D Q IN CLK Clk IN OUT1 OUT2 OUT3 OUT4 OUT Before 1 1 0 0 0 0 0 2 0 1 0 0 0 0 3 0 0 1 0 0 0 4 1 0 0 1 0 0 5 0 1 0 0 1 1 Pattern recognizer • Combinational function of input samples • in this case, recognizing the pattern 1001 on the single input signal

Serial Addition (D Flip-Flop) • Slower than parallel • Low cost • Share fasthardware onslow data • Good for multiplexed data

Serial Addition (D Flip-Flop) • Only one full adder • Reused for each bit • Start with low-order bit addition • Note that carry (Q) is saved • Add multiple values. • New values placed in shift register B

Serial Addition (D Flip-Flop) • Shift control used to stop addition • Generally not a good idea to gate the clock • Shift register can be arbitrary length • FA can be built from combin. logic

Universal Shift Register • Clear • Clock • Shift • Right • Left • Load • Read • Control

0 1 2 3 Design of Universal Shift Register • Consider one of the four flip-flops • new value at next clock cycle: • Note slightly different than Mano version (Clear) clear s0 s1 new value 1 – – 0 0 0 0 output 0 0 1 output value of FF to left (shift right) 0 1 0 output value of FF to right (shift left) 0 1 1 input Q[N] Nth cell to N-1th cell to N+1th cell Q D CLK CLEAR s0 and s1control mux Q[N-1](left) Q[N+1](right) Input[N]

Summary • Shift registers can be combined together to allow for data transfer • Serial transfer used in modems and computer peripherals (e.g. mouse) • D flip flops allow for a simple design • Data clocked in during clock transition (rising or falling edge) • Serial addition takes less chip area but is slow • Universal shift register allows for many operations • The register is programmable. • It allows for different operations at different times • Next time: counters (circuits that count!)

Continue Chapter 6, Overview • Counters are important components in computers • The increment or decrement by one in response to input • Two main types of counters • Ripple (asynchronous) counters • Synchronous counters • Ripple counters • Flip flop output serves as a source for triggering other flip flops • Synchronous counters • All flip flops triggered by a clock signal • Synchronous counters are more widely used in industry.

Counters • Counter: A register that goes through a prescribed series of states • Binary counter • Counter that follows a binary sequence • N bit binary counter counts in binary from n to 2n-1 • Ripple counters triggered by initial Count signal • Applications: • Watches • Clocks • Alarms • Web browser refresh

Binary Ripple Counter • Reset signal sets all outputs to 0 • Count signal toggles output of low-order flip flop • Low-order flip flop provides trigger for adjacent flip flop • Not all flops change value simultaneously • Lower-order flops change first • Focus on D flip flop implementation

Another Asynchronous Ripple Counter • Similar to T flop example on previous slide

A3 A2 A1 A0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 1 0 0 0 1 0 0 1 Asynchronous Counters • Each FF output drives the CLK input of the next FF. • FFs do not change states in exact synchronism with the applied clock pulses. • There is delay between the responses of successive FFs. • Ripple counter due to the way the FFs respond one after another in a kind of rippling effect.

Synchronous counters • Synchronous(parallel) counters • All of the FFs are triggered simultaneously by the clock input pulses. • All FFs change at same time • Remember • If J=K=0, flop maintains value • If J=K=1, flop toggles • Mostcounters are synchronous in computer systems. • Can also be made from D flops • Value increments on positive edge

Synchronous counters • Synchronous counters • Same counter as previous slide except Count enable replaced by J=K=1 • Note that clock signal is a square wave • Clock fans out to all clock inputs

Circuit operation • Count value increments on each negative edge • Note that low-order bit (A) toggles on each clock cycle

Synchronous UP/Down counters • Up/Down Counter can either count up or down on each clock cycle • Up counter counts from 0000 to 1111 and then changes back to 0000 • Down counter counts from 1111 to 0000 and then back to 1111 • Counter counts up or down each clock cycle • Output changes occur on clock rising edge

Counters with Parallel Load • Counters with parallel load can have a preset value • Load signal indicates that data (I3…I0) should be loaded into the counter • Clear resets counter to all zeros • Carry output could be used for higher-order bits

Clear Clk Load Count Function 0 X X X Clear to 0 1 ↑ 1 X Load inputs 1 ↑ 0 1 Count 1 ↑ 0 0 No Change Function Table Counters with Parallel Load • If Clear is asserted (0), the counter is cleared • If Load is asserted data inputs are loaded • If Count asserted counter value is incremented

Binary Counter with Parallel Load and Preset • Presettable parallel counter with asynchronous preset. If PL’ = 0, load P into flops

Binary Counter with Parallel Load and Preset • Commercial version of binary counter

Summary • Binary counters can be ripple or synchronous • Ripple counters use flip flop outputs as flop triggers • Some delay before all flops settle on a final value • Do no require a clock signal • Synchronous counters are controlled by a clock • All flip flops change at the same time • Up/Down counters can either increment or decrement a stored binary value • Control signal determines if counter counts up or down • Counters with parallel load can be set to a known value before counting begins.

Continue Chapter 6, Overview • Circuits do not respond instantaneously to input changes • Predictable delay in transferring inputs to outputs • Propagation delay • Sequential circuits require a periodic clock • Goal: analyze clock circuit to determine maximum clock frequency • Requires analysis of paths from flip-flop outputs to flip-flop inputs • Even after inputs change, output signal of circuit maintains original output for short time • Contamination delay

Clock Period Clock Sequential Circuits • Sequential circuits can contain both combinational logic and edge-triggered flip flops • A clock signal determines when data is stored in flip flops • Goal: How fast can the circuit operate? • Minimum clock period: Tmin • Maximum clock frequency: fmax • Maximum clock frequency is the inverse of the minimum clock period • 1/Tmin = fmax

A Y t c d t p d Combinational Logic Timing: Inverter A Y • Combinational logic is made from electronic circuits • An input change takes time to propagate to the output • The output remains unchanged for a time period equal to the contamination delay, tcd • The new output value is guaranteed to valid after a time period equal to the propagation delay, tpd

Combinational Logic Timing: XNOR Gate • The output is guaranteed to be stable with old value until the contamination delay • Unknown values shown in waveforms as Xs • The output is guaranteed to be stable with the new value after the propagation delay

Combinational Logic Timing: complex circuits Tpd = 2ns Tcd = 1ns Circuit X Tpd = 3ns Tcd = 1ns A C A Circuit X C B Tpd = 5ns Tcd = 1ns B • Propagation delays are additive • Locate the longest combination of tpd • Contamination delays may not be additive • Locate the shortest path of tcd • Find propagation and contamination delay of new, combined circuit

Clocked Device: Contamination and Propagation Delay D Clk Q t cd t Clk-Q • Timing parameters for clocked devices are specified in relation to the clock input (rising edge) • Output unchanged for a time period equal to the contamination delay, tcd after the rising clock edge • New output guaranteed valid after time equal to the propagation delay, tClk-Q • Follows rising clock edge

Clocked Devices: Setup and Hold Times ts th D Clk Q • Timing parameters for clocked devices are specified in relation to the clock input (rising edge) • D input must be valid at least ts(setup time) before the rising clock edge • D input must be held steady th(hold time) after rising clock edge • Setup and hold are input restrictions • Failure to meet restrictions causes circuit to operate incorrectly

Edge-Triggered Flip Flop Timing D CLK th = hold time ts = setup time • The logic driving the flip flop must ensure that setup and hold are met • Timing values (tcd tpd tClk-Q ts th)

TClk-Q = 5 ns Ts = 2 ns Tpd = 5ns TClk-Q = 5ns X Y D Q D Comb. Logic Z Q D FFB FFA G CLK Analyzing Sequential Circuits • What is the minimum time between rising clock edges? • Tmin = TCLK-Q (FFA) + Tpd (G) + Ts (FFB) • Trace propagation delays from FFA to FFB • Draw the waveforms! Fmax = _______

Tpd = 4ns Q D Comb. Logic F Q D X Y Comb. Logic H Z FFB FFA Tpd = 5ns CLK TClk-Q = 5ns TClk-Q = 4 ns Ts = 2 ns Analyzing Sequential Circuits • What is the minimum clock period (Tmin) of this circuit? Hint: evaluate all FF to FF paths • Maximum clock frequency is 1/Tmin

Tpd = 4ns Q D Comb. Logic F Q D X Y Comb. Logic H Z FFB FFA Tpd = 5ns CLK TClk-Q = 5ns TClk-Q = 4 ns Ts = 2 ns Analyzing Sequential Circuits Fmax = _______ • Path FFA to FFB • TClk-Q(FFA) + Tpd(H) + Ts(FFB) = 5ns + 5ns + 2ns = 12ns • Path FFB to FFB • TCLK-Q(FFB) + Tpd(F) + Tpd(H) + Ts(FFB) = 4ns + 4ns + 5ns + 2ns

Q D Q D Analyzing Sequential Circuits: Hold Time Violation Th = 2 ns Tcd = 2ns Tcd = 1ns X Y D Comb. Logic Z FFB FFA G CLK • One more issue: make sure Y remains stable for hold time (Th) after rising clock edge • Remember: contamination delay ensures signal doesn’t change • How long before first change arrives at Y? • Tcd(FFA) + Tcd(G) >= Th • 1ns + 2ns > 2ns

Tcd = 1ns Q D Comb. Logic F Q D X Y Comb. Logic H Z FFB FFA Tcd = 2ns CLK TClD = 1ns TClD = 1 ns Th = 2 ns Analyzing Sequential Circuits: Hold Time Violations All paths must satisfy requirements • Path FFA to FFB • TCD(FFA) + TCD(H) > Th(FFB) = 1 ns + 2ns > 2ns • Path FFB to FFB • TCD(FFB) + TCD(F) + TCd(H) > Th(FFB) = 1ns + 1ns + 2ns > 2ns

Summary • Maximum clock frequency is a fundamental parameter in sequential computer systems • Possible to determined clock frequency from propagation delays and setup time • The longest path determines the clock frequenct • All flip-flop to flip-flop paths must be checked • Hold time are satisfied by examining contamination delays • The shortest contamination delay path determines if hold times are met • Check handout for more details and examples.