Pulse Generator

Pulse Generator. High Speed Digital Systems Lab Winter 2007/08 Project definition Instructor: Yossi Hipsh Students: Lior Shkolnitsky, Yevgeniy Lobanov. Topics. The main goal I/O scheme Specifications definition Block diagram (preliminary) Time table of the project. The main goal.

Pulse Generator

E N D

Presentation Transcript

Pulse Generator High Speed Digital Systems Lab Winter 2007/08 Project definition Instructor: Yossi Hipsh Students: Lior Shkolnitsky, Yevgeniy Lobanov

Topics • The main goal • I/O scheme • Specifications definition • Block diagram (preliminary) • Time table of the project Pulse Generator

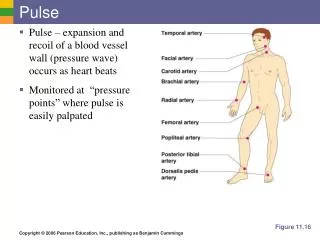

The main goal • To build a Programmable Pulse Generator. • The Generator will be integrated into an existing lab experiment, that teaches about High Speed Systems Phenomena: reflections, skew and jitter. • The Generator will create a delta signal (very short pulse) and pulse signal into transmission line. • This will allow a better way to observe reflections. Pulse Generator

Short pulse (delta) Function selection Long pulse (step) Power supply I/O scheme Programmable Fast Pulse Module Pulse Generator

Specifications definition OUTPUTS • Short pulse width: 0.5 to 1 nSec • Long pulse width: 10 to 13 nSec • Very fast rising/falling edge: ~130 pSec • Pulses repetition: 0.1-1 µSec (1-10 MHz) • Stable period (low jitter): <10psec peak-to-peak INPUTS • Function selection: • Control of the pulse width: 10pSec steps • 32 fixed pulse widths, changed by switch, to provide different results for different students • Power supply: +2.5 to +5 Vdc Pulse Generator

Power Supply Programmable Delay Splitter Oscillator AND Programmable Delay Buffer Controller Block diagram (preliminary) An option: to use a two channel delay unit - NB6L296M. Pulse Generator

Time table of the project Pulse Generator

Questions / Answers Thank you! Pulse Generator

Backup Pulse Generator