Advanced Timing Control System for Beamline Synchronization

E N D

Presentation Transcript

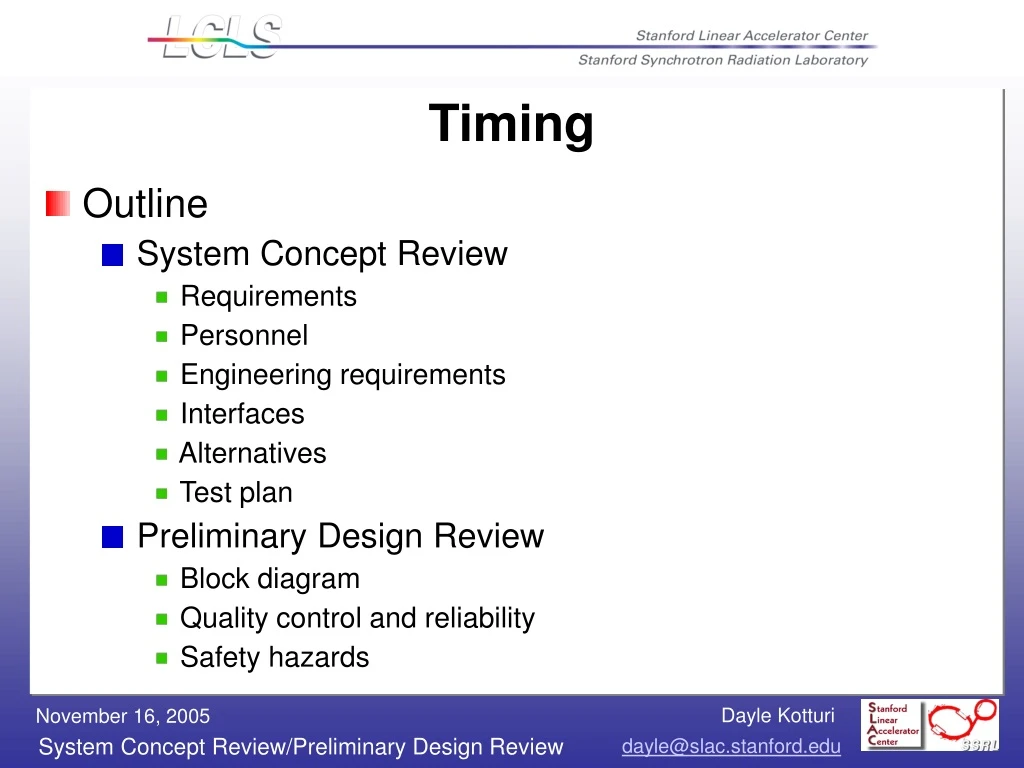

Timing • Outline • System Concept Review • Requirements • Personnel • Engineering requirements • Interfaces • Alternatives • Test plan • Preliminary Design Review • Block diagram • Quality control and reliability • Safety hazards

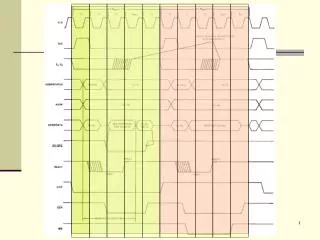

Requirements • Timing triggers are sent to devices to synch acquistions and measurements down the beamline • Triggers are synched to the RF clock • Input timing patterns (PNET SLCNET) arrive at 360 Hz, 1/120 sec in advance of when they are executed • Late updates (during 1/120 sec prior to execution), for eg, MPS status updates, are also accepted • Pnet pattern does not include everything. Eg. EPICS timestamp, LCLS MPS rate-limit must be appended on.

Personnel • Customers = Patrick Krejcik + Paul Emma need timing control system thru BC1 by Dec 06 • Hardware = Dave Brown, COTS products • Software = Dayle Kotturi

Engineering Requirements • As per requirements slide !?

Interfaces • PNET to LCLS MPG • 128 bit pattern @ 360 Hz including PP, YY, incl/excl mask and a 4 bit countdown to pulse id rollover • LCLS MPG to EVG • MPS to LCLS MPG • EVG to EVRs • EVRs to EVR transition modules • EVR transition modules to devices

Alternatives • PNET SLCNET is unique to SLAC. No VME COTS modules exist. VME PNET Receiver had to be built and device driver written to meet Controls Group VME standard • Given VME PNET Receiver, COTS products could then be used to propagate the timing info to devices. To take advantage of existing hardware modules and EPICS software, we chose to follow SLS and Diamond

Quality control and reliability • PNET Receiver was tested over the summer for weeks at a time to look for dropped packets. Device driver performs checksum-like tests on front of pattern, end of pattern and front-to-end synching. If any of these 3 types of errors are found, counter is incremented, but comparator is reset to current value and operation continues.

Safety hazards • 110V AC Connector • Require “Electrical Safety 251” completion for plugging/unplugging • Hazards - Shock • Mitigation - Don’t touch conductors when plugging into outlet • Multi-mode fiber optic cable • Don’t look directly into cable to determine presence of signal