Semiconductor Process Integration and Reliable Design Overview

360 likes | 426 Views

Learn about process integration, electro migration, reliability, scaling, and electrical structures in semiconductor design. Understand the challenges and optimizations in achieving a reliable chip design.

Semiconductor Process Integration and Reliable Design Overview

E N D

Presentation Transcript

Integration Design and Process Integration

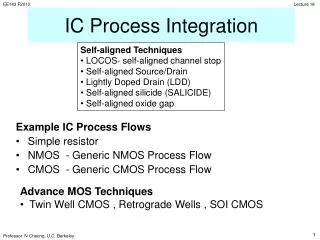

Overview • Integration • Matching/ Accommodating different processes to obtain a ‘passing’ or good chip • Process Integration • Design/ Process Integration • Modifying the design (slightly), to suit the process • Usually, the electrical circuit is not altered • Assumes that process has been developed or optimized to the maximum possible extent • Always remember that the cost /benefit is the ‘bottom line’

Index • Miscellaneous • Electro migration • Scaling in MOS • Electrical Structure (mostly FEOL) • BEOL Cu vs Al and Low-K vs Oxide

Electro migration • Due to movement of electrons, the atoms in a very small line move • formation of voids, increase in electrical resistance, complete breakdown • hillocks, whiskers ==> shorts • Minimum length needed “Blech Length” for a given current density • Depends on the material • Copper, Gold good electromigration resistance • Reliability issue

Electro migration • Mean Time to Fail (MTF) depends on Current Density (J) • Current Density few million Amp/sq cm • Grain size: • movement along grain boundaries faster • For very small lines, grain size = line width • if av grain size is 1 um, a 10 um line will fail quickly (for the same current density, a 1 um line will fail later, a 0.5 um line may fail more quickly) • also depends on arrangement and orientation of grain

Electro migration • Al is more prone to electromigration, however... • Cu does not form a stable strong oxide • Delamination from the liner is an issue • EM failures in copper likely to be in the interface, in Al, in the bulk • Also, W has very high resistance to electromigration • Length of a path may not become very high • In Cu, (especially with dual damascene), for the same design, length may become more

Reliability • Infant Mortality regime (components of poor quality) • Working life Regime • Wear Out regime Fail/unit time • Arrhenius equation • High Temp Operation Test - HTOT • Highly accelerated Stress Tests (HAST): - high humidity, high temp Time

Reliability • Different mechanisms of fail may have different activation energies • ==> Bimodal distribution of fails Cumulative % Fails Temp • Arrhenius equation is suitable for chemical reactions • Not always suitable for explaining physical failure mechanisms

Scaling • Scaling: If you reduce all the features (or some set of parameters) by a constant factor, will the performance be similar? Better? Worse? • Eg. Important dimensions are TOX, L, X L Gate TOX Source Drain X Depletion Region

Scaling • Information from W. Maly: Atlas of IC Technologies • If all dimensions are reduced by 2 (for example) CS0 CS L/2 TOX/2 Gate X/2 X/2 • With same diffusion process, to obtain a shallower junction, need to start with lower initial concentration • ==> very high sheet resistance (shallow Jn, low dopant)

Scaling • If only some dimensions are scaled • eg. TOX and L, but not Junction depth CS0 L/2 TOX/2 Gate X X • Depletion regions merge, short channel

Scaling • If dimensions are scaled and dopant concentration “increased” CS CS0 L/2 TOX/2 X Gate X/2 X/2 • Tolerable sheet resistance • ==> High gradient of dopant in the Jn (hot electron effect) ==> LDD etc

Scaling • Constant Field : • Reduce a physical dimension by ‘k’ , then reduce the voltage also by k • This reduces drain current, gate delay and gate-channel capacitance by k • Number of circuits/ sq cm increases by k2

Scaling • Power per unit area remains constant • in CMOS. NMOS and Bipolar do not follow this scaling rules ==> Issues • Power Delay product (PDP) • NOTE: Total power, not power per unit area: • Reduces by cubic • Practical Limitations by processes (eg. Litho resolution, alignment, process marginalities)

Metal Gate • MOS: using metal gates: Gate oxide etch/growth N N Si N N N N Source/Drain Diff and oxide growth Contact Etch

Metal Gate Gate Source Drain N N N N Metal Dep Metal Etch • Minimum Feature Size is 2l • Alignment tolerance l • Based on the above steps, only 5% of the area is used for transistor channel • Overlap of gate to source and gate to drain ==> capacitance

Poly Gate • MOS: using poly gates: • Active Mask (STI for example) • Poly dep/etch/ implantation (self aligned) • Contact formation • --- Withstands high temp • Active channel area is about 12% of total area • lower capacitance • better channel definition • one more interconnect layer (poly)

Electrical Structures • Electrical Structures: • Resistor: • Poly (silicided) for low resistance and unsilicided for high resistance • silicided: 5 to 10 ohm/square • unsilicided 300 to 500 ohm/square (depends on dopant level and type) • undoped silicon (intrinsic) very high resistance, not usually used • Can be ‘created’ during gate formation

Electrical Structures • Active (source/drain) areas can also be used for high resistance • Ohmic vs Schottky contact for lightly doped n structure • P type or highly doped N type • CAPACITOR: • MOS capacitor, similar to transistor • In the BEOL in some cases (Metal Insulator Metal Capacitor ) (Use Al for better thickness control) • Deep Trench capacitor (FEOL) for DRAM

Electrical Structures • INDUCTOR: • Metal ‘circle’ • Inductance related to number of turns, radius etc • Parasitic resistance, capacitance • BEOL • Diode: • PN Junction diode • Schottky Diode • high reverse bias current • Many ‘slotted’ N+ in P well, with merging depletion region, for good reverse bias current (appears as PN in reverse, as Schottky in fwd)

FEOL Flow-I • Review • Sequence with more detail than what we saw before • Start with bulk P type silicon • Oxidize and strip (obtain clean surface) • Pad oxide and Nitride • Trench Lithography • Active (source drain) and gate area definition • CD measurement for example • Trench Etch • post etch CD measurement • etch bias

FEOL Flow-II • Trench Etch • blind etch • less than a micron depth • post etch CD measurement • etch bias

FEOL Flow-III • Trench oxidation (very small thickness) • TEOS Dep (0.5 micron for example, above active)+ Anneal • Reverse Active Mask: Litho, etch (about 0.5 micron) • To reduce the ‘load’ on STI CMP • load here means planarization load, NOT the removal load • STI CMP • target 0.5 micron removal on small active (faster polish area) for example • Other integration LOCOS • OR modification of STI by Poly Dep+CMP .... • Nitride Removal

FEOL Flow-IV • Pad oxide removal • Sacrificial oxidation (10 nm) • Nwell implant • Pwell implant • Gate Oxidation • Poly deposition (perhaps thin cap oxide for hard mask) • Gate Litho(use ARC)/ Etch • NMOS implant (LDD, Halo): Not the main implants • PMOS implant (LDD, Halo): Not the main implants • RTP

FEOL Flow-V • Spacer Formation • Nitride • Spacer etch • NMOS (main) implant • PMOS (main) implant • RTP • If you need unsilicided areas, you need to mask them with oxide/nitride • Pre-silicide clean (eg. Sputter the surface, or light chemical etch) • Co dep • Anneal (about a minute, 500 C) • Un-reacted Co removal • Nitride Dep (for contact etch)

FEOL / BEOL • BPSG Dep + Anneal + CMP (0.5 um thick remaining) • Cap Ox (to withstand W CMP in the next steps) • Contact photo + etch • Ti/TiN Liner dep (IMP Ti, CVD TiN) • W CVD • W CMP • ILD/PMD Oxide for Copper, Barrier Dep for Al

BEOL (Aluminum) • Barrier Dep (Ti/TiN) • Al Dep (PVD) + Ti/TiN • Al Photo + Etch (M1 levl) • Oxide Dep • Oxide CMP (blind) • Via12 etch and so on...

BEOL (Copper) • Oxide Dep • M1 photo + Etch • Liner (Ta/TaN) Dep • Cu (seed + electrochem) Dep • Cu CMP • Nitride (via etch stop layer) dep • Oxide Dep • V12-photo + etch (stop on nitride) • M2 photo + etch (blind) and so on... • OR M2 photo + blind etch followed by V12-photo+ stop on nitride etch

BEOL (Copper) • Via first integration • Resist removal from the bottom of via can be an issue • Metal first integration • Resist pooling an issue • Some Other schemes: • Single damascene • Intermediate (stop on) nitride • increased cost, lower throughput

BEOL Integration • Some Issues: • Over etch: defectivity • under etch: opens • etch uniformity (center edge) • CMP • In Copper CMP, too much dishing/erosion ==> oxide needs to be planarized • increased cost

Low -K • Oxide vs Low K • For RC delay reduction • Need • thermal stability • chemical inertness (selective etch) • mechanical strength (for Cu CMP) • adhesion to barrier • low stress • Thermal expansion matching • low diffusivity of contaminants (or copper)

Low -K • Only if k < 3, it is considered as ‘real low-k’ • FSG (fluorinated silicate glass) (k=3.5) • not very low • absorbs water (can create HF and hence havoc) • Carbon Doped Silica (k = 3) • commercial: AMAT Black Diamond , NOVELUS Coral • uniform carbon doping is an issue • Organic polymers • low k, but soft (mechanical strength), temp stability, chemical reactivity (photoresist etc) • thermal expansion mismatch ==> crack

Low -K • Organic polymers • low k, but soft (mechanical strength), temp stability, chemical reactivity (photoresist etc) • thermal expansion mismatch ==> crack • low thermal conductivity ==> more stress on metal • Adhesion, Delamination • eg. PTFE adhesion, delamination during CMP • Absorbance of chemicals during process • and subsequent release • --> metal lines and transistors affected • DLC (diamond like carbon) • etch etc not tested

Low -K • Porous silica (or other materials) • Thermal, chemical stability is good • Diffusion of materials is high • Mechanical strength (CMP) may be an issue • Absorbance of chemicals an issue • Good thermal insulator ==> very high stress on metal • --> need to take heat conduction path in design • Repeatability (of process and material quality) etc need to be tested • New material: Not tested very well yet

Low -K • CAP layer used to ‘increase’ mechanical strength • eg SiC. (Has high K, so only very thin films can be used) • DLC may also be used