Address Decoding

Outline Address Decoding Strategy Full Address Decoding Partial Address Decoding Block Address Decoding Address Decoder Design Goal Understand address decoding schemes Understand address decoder design Reading Microprocessor Systems Design, Clements, Ch. 5.1-5.2. Address Decoding.

Address Decoding

E N D

Presentation Transcript

Outline Address Decoding Strategy Full Address Decoding Partial Address Decoding Block Address Decoding Address Decoder Design Goal Understand address decoding schemes Understand address decoder design Reading Microprocessor Systems Design, Clements, Ch. 5.1-5.2 Address Decoding

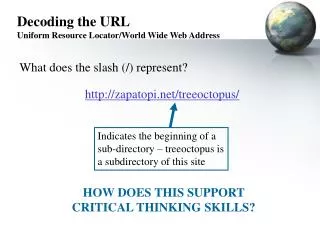

Map memory to address locations “memory” can be peripheral Implement mapping the address decoder Block mapping memory block spans consecutive addresses feed low-order address bits to chip address inputs memory block is aligned decode high-order bits for chip selects deselected chip tristates data I/O memory block chip selects must be mutually exclusive otherwise chips will fight data bus during read cycle multiple locations will be written on write cycle Address Decoding Strategy

Each memory location corresponds to one address no “don’t care” address bits must decode all address bits use all high-order bits to control chip selects all low-order bits go to chip address inputs Example 2 2Kx16 memory chips at $000000-$000FFE and $001000-$001FFE - word addresses A23-A12 = 000000000000 for first block select A23-A12 = 000000000001 for second block select A11-A01 - feed into chip address inputs Full Address Decoding

Memories 10KW ROM 2KW block (ROM1) + 8KW block (ROM2) 2KW RAM 2 words for peripheral 1 (PERI1) 2 words for peripheral 2 (PERI2) Mapping make aligned blocks arbitrary location except ROM1 start at $000000 for reset ROM1 at $000000-$000FFE ROM2 at $00400-$007FFE RAM at $001000-$001FFE PERI1 at $008000-$008002 PERI2 at $008004-$008006 Full Addressing Example

Some address lines not decoded “don’t care” values multiple addresses have same decoding example - 2 2Kx16 memories use A23 to select memory memories are mapped multiple times in memory Advantage cheap Disadvantage multiple mapping - accidental illegal memory access should just have bus error instead Partial Address Decoding

Partial decoding decode high order bits (by convention) feed low order bits to chip address inputs don’t care about middle bits Decoding ROM1 select at A23-A21 = 000 RAM select at A23-A21 = 001 ROM2 select at A23-A22 = 01 PERI1 select at A23-A22 = 10 PERI2 select at A23-A22 = 11 Better scheme - less address space waste ROM1 select at A23-A20 = 0000 RAM select at A23-A20 = 0001 ROM2 select at A23-A21 = 001 PERI1 select at A23-A21 = 010 PERI2 select at A23-A21 = 011 nothing when A23 = 1 Partial Decoding Example

Divide address space into blocks Fully decode each block using high order bits single-chip decoders available e.g. 4 to 16-line decoder - divide space into 16 blocks 512KB blocks for 68000 Optionally subdivide within block by cascading decoder chips with more address inputs Feed some low-order address bits to chip address inputs Put memory device at each block start Block Address Decoding

Full address decoding for large block e.g. decode A23-A17 for 64KB block Block decoding within block divide 64KB into 16 4KB blocks using A16-A13 and full decoder enable Partial decoding within subblock e.g. locate PERI1 and PERI2 within a 4KB block Goals minimize address space waste minimize decoder cost, time delay Mixed Decoding Schemes

Approaches random logic m-to-n-line decoder PROM programmable logic array (PLA) programmable array logic (PAL) field programmable gate array (FPGA) Issues cost chip count speed ease of modification Address Decoder Design

Implement decoding in SSI gates boolean function to recognize address Fast Could take many chips Not easily modified Best suited for very simple partial decode Not used in most systems Random Logic

Convert m-bit binary code to one of n outputs n = 2m Common types 74LS154 - 4-to-16-line decoder 74LS138 - 3-to-8-line decoder 74LS139 - dual 2-to-4-line decoder active low outputs since memory chip selects are active low often have additional enable inputs permits decoders to be cascaded output of one enables another Issue time delay in cascade feed AS* into last set of decoders M-To-N-Line Decoder

4 4Kword ROM blocks starting at $000000 8 1Kword RAM blocks starting at $020000 8 peripherals using 8 words in the range $010000 to $01007F Used some NOR gates to save some decoders Delay to last enable is IC1a NOR + IC2 decode + IC4 enable delays enable delay is usually faster than decode delay if faster than address to AS* delay, then total delay is only AS* enable delay of final 74LS138 chips address to AS* delay is > 30ns on 68000 74LS138 Example

PROM = programmable ROM m address inputs p data outputs Chip select input Put 1 of 2m p-bit words on output when selected a lookup table must implement decoding truth table directly Problem decoding lots of address bits => big PROM 2KB blocks requires a 64 Kbit PROM for 68000 But very flexible PROM Decoding

Minimum space per ROM/ROM now 2KB, fully decoded, can expand to 8KB 2KB peripheral space divided into 8 peripherals ROM1 - 2 2Kx8 at $000000-$000FFF ROM2 - 2 2Kx8 at $001000-$001FFF ROM3 - 2 2Kx8 at $002000-$002FFF RAM1 - 4 1Kx4 at $00C000-$00C7FF PERI1 - 256 bytes at $00E000-$00E0FF PERI2 - 256 bytes at $00E100-$00E1FF PERI3 - 256 bytes at $00E200-$00E2FF PROM Decoding Example

PROM outputs tristate when chip deselected use resistor pullups so outputs go high then this deselects memories Use random logic to decode A23-A16 = $00 Use PROM to RAM/ROM and peripheral pages Use 74LS138 to decode within peripheral page note: must access peripheral page synchronously put 8-bit peripherals on upper byte Use additional decoders for upper/lower ROM byte select during read PROM Decoding Example (cont.)

FPGA != FPGA FPGA in this chapter not the same as Xilinx or Actel bag of programmable gates here FPGA means a programmable m-to-n-line decoder Generate n different products of m bits 82S103 - 9 products of 16 bits can address 256 byte blocks in 24-bit address space can have “don’t care” bits in products be careful outputs are mutually exclusive if used directly as chip enable FPGA Decoding

PLA - programmable logic array FPLA - field programmable logic array n inputs, k products, m outputs can form k different products of n inputs can form m different sums of the products can have “don’t care” bits in products an FPGA with an OR matrix to form sums of products PLA Decoding

PAL - programmable array logic PLA with fixed OR plane each product can only participate in some outputs each output can use only some products usually adequate for decoding faster, cheaper variety of OR plane designs available PAL Decoding

CS address decode is essentially a software-programmable PROM for 8 blocks Base Address Register (CSCR) matches against A<31:16> sets base address of decoded memory block Mask Register (CSMR) CSMR<31:16> is base address mask (BAM) BAM bit = 1 means same bit in CSCR is don’t care don’t care means do not consider in match Example CSCR = $4000 = 0100 0000 0000 0000 - 64 KB block BAM = $0003 = 0000 0000 0000 0011 address checked is 0100 0000 0000 00XX - 256 KB block ColdFire Chip Select Logic