Altera Excalibur

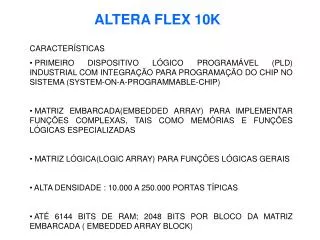

Altera Excalibur. DOCUMENTAÇÃO!!!!. Ambiente de Hardware. Ambiente de Software. Ambiente de Simulação. Sistema de Prototipação Excalibur. Placa de desenvolvimento Excalibur. Placa de desenvolvimento Excalibur. Dispositivo APEX. Características nº de portas - 211.000 13KB de RAM

Altera Excalibur

E N D

Presentation Transcript

Ambiente de Hardware Ambiente de Software Ambiente de Simulação Sistema de Prototipação Excalibur

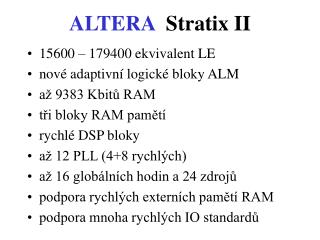

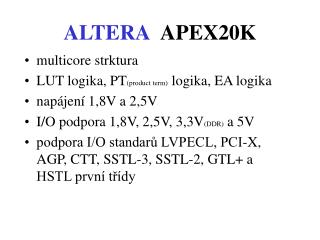

Placa de desenvolvimento Excalibur Dispositivo APEX • Características • nº de portas - 211.000 • 13KB de RAM • nios ocupa entre 25% e 35% da lógica do dispositivo • Modo de programação • conexão JTAG (Quartus II) • memória flash

Placa de desenvolvimento Excalibur Memória Flash • Características • 1Mbyte (512Kb x 16 bits) • Propósito • usada como memória não volátil pelo Nios (w/r) • configuração do APEX (controle de configuração)

Placa de desenvolvimento Excalibur Memória SRAM • Características • 256Kb (64Kb x 16 bits) em cada chip • Nios pré-carregado (64Kb x 32 bits)

Placa de desenvolvimento Excalibur Conectores SODIMM • Características • socket de 144 pinos SODIMM • módulo SDRAM (64bits) • Conectada ao APEX • nios pré-carregado não faz uso desta memória

Placa de desenvolvimento Excalibur Pinos de expansão • Características • 3.3 V e 5 V • O APEX esta protegido dos pinos de 5V por chaves analógicas • Para conexão de placas filhas, como Ethernet

Placa de desenvolvimento Excalibur Conectores PCI (PMC) • Características • APEX PCI • padrão IEEE 1386

Placa de desenvolvimento Excalibur Conectores JTAG • Características • compatível com ByteBlaster e MasterBlaster • Propósitos • programar o APEX (Quartus II) • reprogramar o EPM7064 (Quartus II ou MAX+PLUS II)

Placa de desenvolvimento Excalibur Chaves • Características • compatível com ByteBlaster e MasterBlaster • Propósitos • programar o APEX (Quartus II) • reprogramar o EPM7064 (Quartus II ou MAX+PLUS II) • PCM software (host)

Placa de desenvolvimento Excalibur Controlador de Configuração • Propósito • configurar o APEX • Dados de configuração • Quartus hexout flash (ocupa 1/4 da mem. Flash) • GERMS flash • Configuração de usuário x fábrica • 512Kb - instruções do Nios e espaço de dados não volátil • 256Kb - configuração do usuário • 256Kb - configuração de fábrica

Placa de desenvolvimento Excalibur Entrada/Saída básica • Elementos • push-button switches • dip switch • display de 7 segmentos

Placa de desenvolvimento Excalibur Chaves especiais • Sw2 (reset) • flash APEX • Sw3 (clear) • depende da configuração do APEX • Nios pré-carregado passa a executar o código a partir do endereço 0

Placa de desenvolvimento Excalibur Circuito de clock • Elementos • oscilador (33.333 MHz) • distribuidor de clock

Placa de desenvolvimento Excalibur Circuito de clock • Elementos • oscilador (33.333 MHz) • distribuidor de clock • Dispositivos com clock • APEX • pinos de expansão • conectores PCM • conectores SODIMM

Altera PLD Fluxo de projeto Configuração do processador Biblioteca de periféricos Seleção dos periféricos Hardware Software • Projeto do processador (Verilog / VHDL) • Test Bench para simulação • C Header files • Custom Library • Boot monitor Generate JTAG Serial Ethernet Arquivo de configuração de hardware Código executável Cygnus/Red HatGNUPro SíntesePlace & Route Download & Debug • Projeto do usuário • IP proprietários • Código do usuário • Biblioteca S/W • RTOS

SRAM PBM IRQ CPU FLASH Timer Porta Serial UART Nosso projeto aqui Altera PLD Processador Nios • Processador Soft Core Configurável (Firm Core) • Arquitetura RISC 32-Bit • Instruções de 16-Bit • Maioria das instruções executadasem1 ciclo de clock • Pipeline de 5 estágios • Grande Banco de Registradores Internos • 128, 256 or 512 registradores • 32 registradores por janela • Bloco de Dados Configurável • 16 bits • 32 bits • inclusão ou não de multiplicação

Processador Nios • Faixa de endereçamento • 128 kbytes (16 bits) • 4 Gbytes (32 bits) • Desempenho : até 50 MIPS • Otimizado para PLD APEX • 13% do APEX EP20K200E - 16 bits • 20% do APEX EP20K200E - 32 bits • Freqüência Máxima de 50 MHz • Endereço Base do Vetor de Exceções • 64 endereços de manipuladores de exceções • Nios 32 bits = 4 bytes • Nios 16 bits = 2 bytes • Operações de deslocamento com número de ciclos parametrizável • 1, 3, 7, 15 or 31 Bits/Clock

Parâmetros do Nios • Data Path (32 or 16) • Tamanho do Barramento de Endereços (10 a 33-bits) • Tamanho do Bloco de Registradores (128, 256 or 512) • Endereço de Reset • Endereço Base do Vetor de Exceções • 64 endereços de manipuladores de exceções • Nios 32 bits = 4 bytes • Nios 16 bits = 2 bytes • Bit Shift Speed (1, 3, 7, 15 or 31 Bits/Clock) • Opções de Multiplicação

Banco de Registradores por Janela • Até 512 registradores de propósito geral • Janela móvel permite acesso a 32 registradores por janela • 8 registradores globais (fixos) • 24 registradores (móveis) • Automaticamente usado pelo compilador (C) • Vantagens: • passagem de parâmetros • chamada rápida a subrotinas

0 Clock 1 (Shift 7 bits) Clock 2 (Shift 2 bits) Bit Shift Speed • Múltiplos deslocamentos em um único ciclo de clock • Incrementos de até 3, 5, 7, 15, ou 31 Bits por clock • Caro (área ocupada) • Exemplo: • Bit Shift Speed configurado para 7: i << 9; /* Shift Left by 9 Bits */ • Executa em 2 Clocks

Opções de Multiplicação • Software • Usa a biblioteca matemática do GNU • MSTEP • Hardware Multiplicador • multiplicação de 1 bit por clock • Aumento de ~ 4X sobre a rotina de multiplicação (software) • MUL • Hardware Multiplicador • 16 x 16 32 em 2 Clocks LEs Adicionais Ciclos de Clock16x16>32 Ciclos de Clock32x32>32 Multiplicador Software MSTEP MUL 0 +200 +400 80 18 2 250 80 16

Introdução • Objetivos do Avalon: • simplicidade • operações síncronas • baixo consumo de área (LE) • Para uso “on-chip” • Barramento multimestre mestre (nios 2.0) • Periféricos mapeados em memória

Funções do Barramento • Decodificação de endereço • Geração de chip-select • Multiplexação de barramento de dados • Transferência de dados do mestre para o periférico escolhido • Geração de wait-state • Ciclos de clock extra • Dimensionamento dinâmico de barramento • Suporta periféricos com barramento de dados menor que o tamanho do barramento de dados do avalon • Controle de interrupção • Com prioridade

Sistema Altera PLD Perif. Interno (timer) I/O Nios CPU Perif. Interno (UART) I/O Perif. Externo (memória) User I/F Avalon Bus Perif. Externo (hardware do usuário) User I/F User HW Nios System Module

Temporização do Barramento • Sinais “registered” (sem atraso comb.) • Sinais combinacionais (com atraso comb.) • Informações IMPORTANTES para construção de um wrapper entre avalon e HW do usuário D Q Lógica clock D Q Lógica clock

Cíclos de Leitura do Nios • 0 wait-state, 0 setup/hold time (asinc. perif) • 1 wait-state, 1 setup/hold time (sinc. perif) Nios Address, readn NIOS Avalon CS Data Hw HW

Cíclos de Escrita do Nios • 0 wait-state, 0 setup/hold time (asinc. perif) • 0 wait-state, 1 setup/hold time (sinc. perif)

User-Defined Interface Altera PLD I/O Nios CPU I/O User I/F Avalon Bus User I/F User HW Nios System Module • Criação de portas para interface com outros periféricos • On-Chip & Off-Chip • Configuração de temporização do barramento

Criando um Projeto • Agora vamos criar um projeto com uma interface para ligar um hardware do usuário • Copie o projetominimal_32 do diretório de exemplos do excalibur para o seu diretório • Abra o seu projeto • Dê um duplo click em no bloco nios_system_module

Interface do Usuário 4 1 2 3 1. Código do usuário mais wrapper 2. Seleciona o top 3. Varre o VHDL para as portas - scan files 4. Manualmente escolhe o tipo da porta no barramento Avalor (Type) 5. Finish

Temporização • Neste caso, 1 wait state

Finalizando a integração • Atualize o símbolo do processador com os sinais recém-criados • selecione o símbolo e com o botão da direita “update symbol or block” • crie um símbolo para o hw externo • file--> open para abrir o VHDL e depois em tools criar o símbolo • selecione wr_880 • conecte o wr_880 ao processador

Sintetizando Sintetize o SOC!

Realizando o download 1 4 2 3

Executando o Nios SDK • Ir para o diretório do projeto (...minimal_32/cpu_sdk/src) • Coloque o fonte • Compile o fonte “nb lfsr32.c” • Execute nr lfsr32.srec