V HDL (1)

Elektrotehnički fakultet, Univerzitet u Beogradu. V HDL (1). Osnovi digitalne elektronike , J . Popovi ć, 2006. Svaki VHDL modul sadrži: ENTITY - opis interfejsa ARCHITECTURE – opis arhitekture sistema Za jedan entity mo že biti definisano više arhitektura. Obnuto ne va ži!.

V HDL (1)

E N D

Presentation Transcript

Elektrotehnički fakultet, Univerzitet u Beogradu VHDL (1) Osnovi digitalne elektronike, J. Popović, 2006.

Svaki VHDL modul sadrži: • ENTITY -opisinterfejsa • ARCHITECTURE – opis arhitekture sistema • Za jedan entity može biti definisano više arhitektura • Obnuto ne važi!

Entity - deklaracija • entity– rezervisana reč • entity-name - naziv koji korisnik dajeza entiti • generic – rezervisana reč, koristi se za definisanje konstanti i parametara koji odredjuju taj modul • čini kod univerzalnijim • nije obavezno definisati generike za VHDL modul • constant-names – nazivi konstanti • constant-type – tip konstante, najčešće: • integer, time

port – rezervisana reč, koristi se za definisanje eksternih signala koji služe kao interfejs • signal-names – nazivi eksternih signala • mode - definiše smer signala, najvažniji su: • in - ulaznisignal • out - izlazni signal • inout – ulazno-izlazni signal • signal-type – tip signala, najčešće: • bit, bit-vector, boolean, character, integer, real, string, time • end – rezervisana reč, obavezna!

Arhitektura VHDL koda • Sastoji se iz: • Deklarativnog dela (koji nije obavezan) • Tela arhitekture gde se opisuje model sistema (između naredbi begin i end)

Architecture • architecture – rezervisana reč • architecture-name- korisnički naziv arhitekture, proizvoljan • entity-name - isto ime koje nosi entity kojem se pridružuje data arhitektura • Eksterni signali se nasleđuju iz port deklaracije entity-ja, a u arhitekturi se mogu deklarisati interni signali • deklaracije i definicije se mogu navesti bilo kojim redom • signal declarations – isto kao kod entity-ja, osim što se se ne specificira modsignala. Ovi signali su vidljivi samo u okviru arhitekture • constants – definicija konstanti • begin – početak opisa arhitekture • end –obavezna reč (naziv arhitekture moze da se izostavi)

Komentari u VHDL kodu • Dobar VHDL kod uvek ima dosta komentara • Komentari započinju simbolima “--” • Mogu biti posebne linije ili u produžetku neke naredbe entity Full_Adder_Complement2 is generic(opSize : Natural; -- size of operands (determines adder size) propDelay : Time := 20ns -- adder propagation delay ); port(operand0 : in STD_LOGIC_VECTOR(opSize-1 downto 0); -- first operand operand1 : in STD_LOGIC_VECTOR(opSize-1 downto 0); -- second operand result : out STD_LOGIC_VECTOR(opSize downto 0) -- result of addition ); end entity Full_Adder_Complement2;

Na početku svakog VHDL koda (pre deklaracije entity-ja) treba napraviti zaglavlje sa komentarima (naziv projekta, kratak opis sistema, autor, datum, verzija, softver koji je korišćen...) --------------------------------------------------------------------------------------------------- -- -- Title : Arithmetic_Units -- Design : DWTCoding -- Author : 0 -- Company : 0 -- --------------------------------------------------------------------------------------------------- -- -- File : Arithmetic_Units.vhd -- Generated : Sat Jun 25 10:15:03 2005 -- From : interface description file -- By : Itf2Vhdl ver. 1.20 -- --------------------------------------------------------------------------------------------------- -- -- Description : -- --------------------------------------------------------------------------------------------------- --------------------------------------------------------------------------------------------------- -- entity Full_Adder_Complement2 : performs 2-operand addition in second complement -- NOTE : operands must be of same size, result is 1 bit longer ---------------------------------------------------------------------------------------------------

Radna biblioteka i paketi • Radna bibliotekaje mesto gde VHDL kompajler skladišti informacije u vezi sa projektom na kome se radi. • Često se automatski kreira i koristi bibliotekawork • Mogu se koristiti i standardne biblioteke kao npr. biblioteka koja sadržiIEEE standard definicije • Paketi (packages): • Deo biblioteke u kome se definišu novi tipovi objekata ili operacija (u odnosu na standardni VHDL) • Vrste objekata koji mogu biti definisani u paketu su: • Signali • Tipovi • Konstante • Funkcije • …

Korisnik može sam da definiše svoj paket, postoje pravila za to (slično pisanju bilo kog VHDL koda) • U dizajnu se može pozivati paket korišćenjem naredbe usena početku dizajna • Na primer: Library IEEE ; use IEEE.std_logic_1164.all; IEEE je ime biblioteke u kojoj fajl pod imenom std_logic_1164 sadrži željene definicije. Sufiks all govori kompajleru da upotrebi sve definicije u fajlu. • Umesto all možemo pisati ime određenog objekta da bismo iskoristili samo njegovu definiciju. use ieee.std_logic_1164.std_ulogic;

Signali • Signali koji čine interfejs sistema uvek se deklarišu u kao port-oviu deklaraciji entity-ja • definiše se naziv, mod (smer) i tip signala • U arhitekturi se mogu deklarisati samo signali koji su interni, vidljivi u okviru te arhitekture • isto kao u slučaju entity-ja, osim što se se ne specificira modsignala • Vrednosti signala se mogu očitavati ili dodeljivati u okviru tela arhitekture

Koncept signala u VHDLu (!!!) • Zasnovan na osobinama signala u električnim sistemima • podržani su pojedinačni signali i magistrale (bit i bit_vector) • podržan rad sa više nivoa signala • svaki signal ima vremenske parametre • Signal ima jedan ili više drajvera • u drajveru se “pamti” istorija signala ili se zadaje “budućnosti” • ako signal ima više drajvera (izvora) može biti tipa: • Std_ulogic (podržava više nivoa signala, ali ne rešava problem više izvora jednog signala) • Std_logic (rešava pomenuti problem) • Na osnovu drajvera se mogu odrediti atributi koji omogućavaju jednostavniji rad sa signalima

Atributi signala S je naziv signala if CLK=’1’ and CLK’event then … -- detekcija uzlazne ivice signala CLK

Varijable • Rezervisana reč:variable • Varijable su slične signalima, ali nemaju fizičku interpretaciju u kolu! • Nije potrebna posebna deklaracijaza varijable u deklarativnom delu arhitekture • Mi ćemo ih deklarisati samo u procesima (mogu biti deklarisane i u nekim drugim strukturama): • Varijable nemaju drajvere i zbog toga ne postoje ni atributi za ovaj tip promenljivih • Njihove vrednosti se menjaju uvek trenutno!!!

Konstante • Pogodne su zbog čitljivosti i održavanja koda • Deklarišu se uvek u arhitekturi: • Za razliku od generika koji se deklarišu u entitiju i vidljivi su u svim arhitekturama vezanim za taj entiti, konstante su vidljive samo u arhitekturi u kojoj je data njihova deklaracija! • Konstanta se sme koristiti bilo gde gde se koristi i vrednost koju ona predstavlja.

Tipovi podataka u VHDL-u • Svi signali, varijable i konstante u VHDL-u moraju imati pridruženi tip. Tip specificira skup ili opseg vrednosti koje objekat može uzimati. • Predefinisani skalarni tipovi podataka koji se najčešće koriste: • Od vektorskih se najčešće koristi bit_vector

Fizički tip podataka podržan u VHDL-u je vreme (TIME) • definisani su i multipli primarne jedinice (npr. ps, ns, us, ms...) • Najkorišćeniji tipovi podataka u VHDL-u su user-defined tipovi i to najčešće enumerated tipa (nabrojivi), koji se definišu listanjem svih vrednosti. • Primer: • Tipovi boolean i character su takođe nabrojivog tipa, kao i std_ulogic tip koji je deo IEEE 1164 paketa !!! Važno

Druga kategorija user_defined tipova podataka su nizovi. Niz se definiše kao uređeni skup elemenata istog tipa, gde je svaki element pozicioniran indeksom u okviru niza. • Primeri:

Operatori (1) • Logički • mogu se primenjivati na podatke tipa: • Bit • Bit_vector • Boolean • rezultat je uvek istog tipa kao operandi • Aritmetički • klasične aritmetičke operacije za podatke tipa: • Integer • Real Aritmetički oper.

Operatori (2) • Relacijski: =, /=, >, <, <=, >= • operandi moraju biti istog tipa i to: • bit, Boolean, character, integer, real, string, time ili bit_vector • rezultat je uvek Boolean tipa (true ili false) • kod poređenja bit vektora, operandi se ravnaju od prvog bita sa leve strane!!! • 1001 je “manje” od 110 • Veoma je važno razlikovati operator “<=“ od istog simbola kojim se dodeljuje vrednost signalu • Primer: a <= b <= c Prvo se izvršava operator koji je desno, tj. signalu a se dodeljuje rezultat poredjenja signala b i c

Operatori (3) • Operatori za šiftovanje “u levo” i “u desno”: • Logičko (upisuje 0 na upražnjeno mesto), aritmetičko (upisuje LSB ili MSB na upražnjeno mesto), rotaciju • Operator vezivanja (simbol “&”) • koristi se za definisanje novih jednodimenzionih nizova tako što vezuje delove ili celenizoveako su operandi istog tipa Uslovne naredbe, petlje • Koriste se naredbe kao u drugim programskim jezicima: • if – then – else (elsif) • case – when • wait, wait until, wait for • for - loop

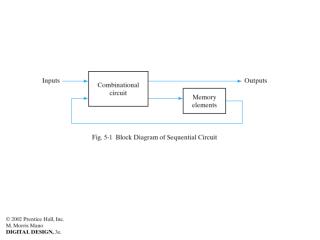

Vrste modela u arhitekturi VHDL koda • Model ponašanja (Behavioral) • “ŠTA sistem treba da radi?” • Opisuje algoritam koji treba da se izvršava • Zasniva se na procesima! • Strukturni model • “KAKO se sistem može realizovati?” • Opisuje strukturu • Zasniva se na: • instanciranju komponenti (pozivanju drugih entity/architecture parova) • mapiranju portova(preslikavanje konkretnih signala na portove komponente koja se instancira) • Ovi modeli se mogu kombinovati u jednoj arhitekturi

architecture behavioral of REG_4 is begin process is variable Dout0Var, Dout1Var, Dout2Var, Dout3Var : bit ; begin if ( clk = '1' and Enable = '1' ) then Dout0Var =: D0 ; Dout1Var =: D1 ; Dout2Var =: D2 ; Dout3Var =: D3 ; end if; Dout0 <= Dout0Var after 5 ns; Dout1 <= Dout1Var after 5 ns; Dout2 <= Dout2Var after 5 ns; Dout3 <= Dout3Var after 5 ns; wait on D0, D1, D2, D3, Clk, Enable; end process; end architecture behavioral ; IF clk = 1 & enable =1 Ažuriraj izlazne signale Čekaj na novu promenu ulaznog signala Model ponašanja

Strukturni model architecture structural of REG_4 is signal gated_clk : bit; begin G1: entity work.and2(vital) port map ( Clk, Enable, gated_clk ); U1: entity work.dff(vital) port map ( D0, gated_clk, Dout0 ); U2: entity work.dff(vital) port map ( D1, gated_clk, Dout1 ); U3: entity work.dff(vital) port map ( D2, gated_clk, Dout2 ); U4: entity work.dff(vital) port map ( D3, gated_clk, Dout3 ); end architecture structural ;

Opis ponašanja sistema u VHDLu • Osnovni element u opisu ponašanja sistema je proces. • Proces je kolekcija sekvencijalnih koraka, a izvršava se konkurentno (paralelno) sa ostalim procesima • Proces se definiše u okviru arhitekture, tako da “vidi” sve signale i konstante koje su deklarisane ili su vidljive u okviru te arhitekture

U procesu se ne mogu deklarisati signali, samo varijable! • VHDL varijabla čuva informaciju o stanju u okviru procesa i nije vidljiva izvan tog procesa • Proces se izvršava kada se promeni neki od signala koji su navedeni u listi osetljivosti tog procesa (sensitivity list) • proces se izvršava polazeći od prve sekvencijalne linije i nastavlja doposlednje • ako neki signal iz liste osetljivosti u toku izvršavanja procesa promeni vrednost, proces se ponovo izvršava od početka • Korektno definisan proces se uvek zaustavlja u nekom trenutku • Dodeljivanje novih vrednosti signalima se vrši isključivo po završetku procesa!!!