Vahemälu (Cache)

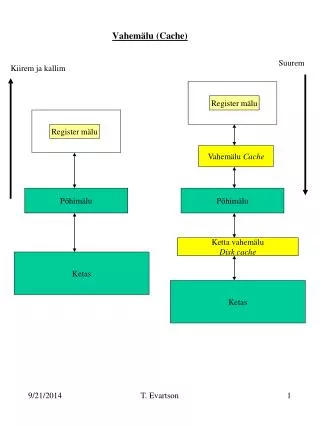

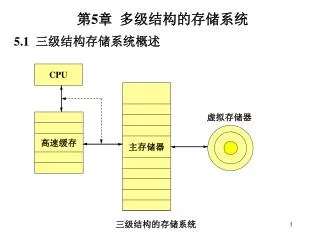

Vahemälu (Cache). Suurem. Kiirem ja kallim. Register mälu. Register mälu. Vahemälu Cache. Põhimälu. Põhimälu. Ketta vahemälu Disk cache. Ketas. Ketas. Vahemälu adresseerimine. Bloki number Block number. Word offset. Register mälu. Sõna edastus Word transfer. Vahemälu Cache.

Vahemälu (Cache)

E N D

Presentation Transcript

Vahemälu (Cache) Suurem Kiirem ja kallim Register mälu Register mälu Vahemälu Cache Põhimälu Põhimälu Ketta vahemälu Disk cache Ketas Ketas T. Evartson

Vahemälu adresseerimine Bloki number Block number Word offset Register mälu Sõna edastus Word transfer Vahemälu Cache Bloki edastus Block transfer Põhimälu T. Evartson

Otsevastavusega vahemälu Direct-mapped cache Vahemälu (Cache) Mälu CPU andmed aadress hit CACHE controller CACHE memory line - minimaalne vahemäluga vahetatav info hulk (4-16 baiti) aadress CPU-st Mälu (Main store) Set Line Word Line 0 Line 1 Set 0 Line 2 Line 3 Line 0 Line 1 Line 0 Set 1 Line 2 Line 1 Line 3 Line 2 Line 0 Line 3 Line 1 Set 2 Line 2 Cache memory Line 3 Line 0 Line 1 Set 3 Line 2 Line 3 T. Evartson

Otsevastavusega vahemälu Direct-mapped cache aadress CPU-st Mälu (Main store) Set Line Word Line 0 Line 1 Set 0 Line 2 Line aadress valib line caches Line 3 Line 0 Line 1 0 Line 0 Set 1 Line 2 3 Line 1 Line 3 3 Line 2 Line 0 2 Line 3 Line 1 Set 2 Line 2 Tag Data Line 3 Line 0 Cache memory Line 1 Set 3 Line 2 Line 3 T. Evartson

Otsevastavusega vahemäluDirect-mapped cache Main Store Mälu CPU data aaddress Line address Set address CACHE memory Line and word address 0 1 2 Cache tag memory 3 Hit Line Tag = T. Evartson

Algus Protsessor pöördub mälu aadressi A poole Leitakse ploki number B kus asub sõna A Kas plokk B on vahemälus Ei Algab ploki B laadimine põhimälust JA Mälu ploki B asukohaks vahemälus määratakse plokk C Sõna A edastatakse CPU-sse Kas plokk Con vaba Ja Ei Asendatakse plokk C plokiga B Kirjutatakse plok B ploki C kohale vahemälus Sõna A edastatakse CPU-sse Lõpp Joon. Vahemälu poole pöördumise algoritm. T. Evartson

Assotsiatiivne vahemäluAssociative mapped cache aadress CPU-st Mälu (Main store) Line 0 Word Tag (Line) Line 1 Line 2 Line 3 Cache memory Line 4 Tag Tag Tag Tag Tag Tag Tag Tag Kõiki tag aadersse võrreldakse paralleelselt (samaaegselt) Line caches võib olla ükstaskõik milline line mälus Line n-1 Assotsiatiivse vahemälu uuendamise strateegiad : • LRU - Least Recently Used • LFU – Least Frequently Used • FIFO – First In First Out (kauem olnud andmed välja) • Järjestikune uuendamine (Round-Robin) • Random - juhuslik Andmete kirjutamine vahemälust põhimällu : • Write-through, korraga muutused kirjutada vahemällu ja põhimälu (486) • Write-back, kirjutatakse põhimällu vahemälu bloki asendamisel, DMA või mõne teise siinihõive õigusega seadme pöördumisel antud aadressil või ka kui ei ole piisavalt kaua andmeid põhimällu kirjutatud (Pentium). Probleem – vahemälu initsialiseerimine pärast RESET-i. Kus on juba vajalik mälust loetud info ja kus juhuslik sisselülitamisel kujunenud kood? Lihtsaim lahendus – lisa bit (dirty bit) initsialiseeritakse resetiga. T. Evartson

Näide Mälu (Main store) 1 Mb aadress CPU-st Line 0 16 baiti iga line Word Tag Line 1 Line 2 Line 3 Cache memory 64 Kb Line 4 Tag Data Tag Tag Tag Tag Tag Tag Tag Line n-1 Line on 16 baiti s.o. neli 32 bitist sõna Mälu on 1 Mb ja seega koosneb 64 K linest Cache koosneb 4096-st linest Et laetud cachesse võib olla laetud ükstaskõik milline 64 K linest on tag 16 bitine T. Evartson

Kogumassotsiatiivne vahemälu Set associative-mapped cache Set associative-mapped cache - kompromiss direct-mapped ja täielikult associative cache vahel Cache 1 Cache 2 Cache 3 Cache 4 Hit Hit Hit Hit 1 Hit Kõik eraldi on direct-mapped caches T. Evartson

Kogumassotsiatiivne vahemäluSet associative-mapped cache Set associative-mapped cache ( kompromiss direct-mapped ja täielikult associative cache vahel) Näide 2-way set assotciative cache. aadress CPU-st Mälu (Main store) Set Line Word Line 0 Line 1 Set 0 Line 2 Line 3 Way 1 Line 0 Line 1 Line 0 Set 1 Line 2 Line 1 Line 3 Line 2 Line 0 Line 3 Line 1 Set 2 Line 2 Tag Data Line 3 Line 0 Way 2 Line 1 Set 3 Line 2 Line 0 Line 3 Line 1 Line 2 Line 3 Tag Data T. Evartson

Vahemälust info leidmise tõenäosus Miss rate Cache capacity Miss rate Block size Direct mapping Miss rate Fully associative mapping Degree of associativity T. Evartson

Info vahemälust mitteleidmise põhjused : • Info blokk ei ole laetud vahemällu (Cold Start Miss, Compulsory Misses) • Ruumi puudus (Capasity Misses) • Konfliktid (Conflict Misses) Ainult otsevastavusega vahemälus. Eraldi käskude ja andmete vahemälu. • Laadimine raske – teist poolt ei saa edasi laadida kui teine on täis. • Kirjutamine lihtsam – käskude mällu ei kirjutata. Virtuaalne vahemälu (virtual Cache). Virtual address bus Physical address bus CPU Memory Management Unit M Virtual Cache Data Bus Füüsiline vahemälu (Physical Cache) Virtual address bus Physical address bus CPU Memory Management Unit M Physical Cache Data Bus T. Evartson

Vahemälu(Cache) tasemed. Level 1 cache - tavaliselt CPU korpuse sees. Käsu peidikmälu (Instruction Cache) umbes 16 Kb ja andmete peidikmälu (Data Cache) umbes 64 Kb. Level 2 cache - väljaspool CPU korpust. Tavaliselt segamini andmed ja käsud. Maht umbes 0,5 kuni 1 Mb. Kolme tasandilise peidikmäluga arvuti Main memory (DRAM) CPU Unified L2 cache Unified L3 cache SRAM Level 1 I- cache Level 1 D- cache CPU package Keyboard controller Graphics controller Disk controller Board level cache (SRAM) Processor board T. Evartson