Outline

Outline. Define Example of a Typical Performance Requirement Define Terms for ATE and DUT Accuracy Describe Effect of Accuracy on Yield and DPM Describe Model Assumptions Example Spreadsheet Calculations Conclusions. Source : Wajil Dalal, Schlumberger. L2 Bus Timing.

Outline

E N D

Presentation Transcript

Outline • Define Example of a Typical Performance Requirement • Define Terms for ATE and DUT Accuracy • Describe Effect of Accuracy on Yield and DPM • Describe Model Assumptions • Example Spreadsheet Calculations • Conclusions Source : Wajil Dalal, Schlumberger

L2 Bus Timing ATE L2Sync_In Window(TATE) Example: 300MHz PPC750 L2 Clock Hi: 3.3ns L2Sync_in to Data Valid: 4ns ATE EPA: 150ps ATE L2 to Window: 4.3ns (Ignoring guardbanding, 6-sigmaquality guarantees, etc.) ATE: L2Sync_In ATE: L2 Output Window DUT: L2 Data Out L2Sync_In to L2 Data ValidTDUT

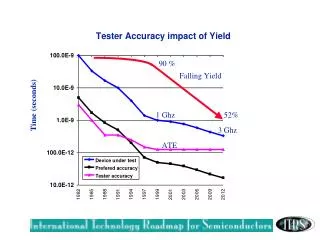

Facts: The Device Under Test will vary in its placement of the driven edge. The ATE will vary in its placement of its driven edges and its compare windows (EPA). The Defects Per Million (DPM) is a measure of how many “bad” devices are incorrectly binned as “good” due to tester in accuracy. The Yield Loss is a measure of how many “good” devices are incorrectly binned as “bad” due to tester inaccuracy. DUT/ATE Accuracy, DPM and Yield Tester edge uncertainty TDUT DUT edge probability Yield Loss DATA Valid DPM TATE Tester T.L - Test Limit Good part Pass Probability of a good part to fail Probability of a bad part to pass Absolute Limit

If yield is <100%: lower tester accuracy, means wider uncertainty box => worse Yield Loss and DPM Loosening the test limit moves the uncertainty box to the right: higher yield but higher DPM. Tightening the test limit move the box to left: lower yield, but lower DPM. $avings EPA effect on Yield and DPM Better EPA Tester edge uncertainty (OTA) DUT edge probability Yield Loss DPM T.L Absolute Limit Worse EPA Tester edge uncertainty (OTA) DUT edge probability Yield Loss DPM T.L Absolute Limit

DUT Assumptions: DUT yield is entirely due to timing inaccuracy; use yield believed due to timing. DUT edge variability is Gaussian (normal) and independent from the ATE edges. 400ps -400ps ATE Window placement probability 1PPM 1PPM +EPA -EPA DUT yield simulation model - Assumptions DUT edge probability Failing DUTs • ATE Assumptions: • ATE Edge Placement Accuracy is Gaussian.. • Tester Edges occur outside the Edge Placement Accuracy spec. <1ppm; we define Overall Timing Accuracy (OTA) = 2 x EPA = 6 x ATEsigma.

DUT Sigma Calculated from Yield • PPC 750 L2 Cache Interface (public document) • Available at 200, 233, 266, and 300MHz. This will look at 266 and 300MHz. • L2 cache interface runs at 33-150MHz • L2Sync_In to L2 Output valid at 266MHz: 5ns • L2Sync_in to L2 Output valid at 300MHz: 4ns • Assumed Bin 1 Yield: 95% • ATE1 EPA: 150ps • ATE2 EPA: 125ps • What is the DUT sigma?