Architecture Wizard and PACE

100 likes | 118 Views

This lab guides how to add a DCM into a PicoBlaze UART real-time clock design to divide the system clock. Learn to configure DCM, assign pin constraints, test in hardware, and interact via hyperterminal.

Architecture Wizard and PACE

E N D

Presentation Transcript

Architecture Wizard and PACE Lab 2 Introduction This material exempt per Department of Commerce license exception TSU

Introduction • This lab guides you through the process of adding a DCM (Digital Clock Manager) into a PicoBlaze UART real-time clock design. • The DCM will divide the 100 MHz system clock on the XUP Virtex-II Pro board down to 50 MHz. • This 50 MHz will clock the design which consists of the PicoBlaze, TX and RX UARTs, and control logic. • You will generate a bitstream and configure the Virtex-II Pro device on the XUP board • You will interact with PicoBlaze via hyperterminal to set the current and alarm times, and start and stop the times. • When the alarm goes off, an LED will flash.

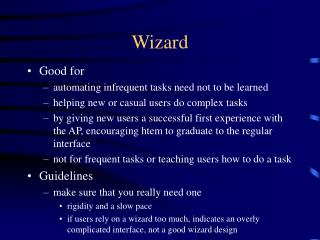

Objectives After completing this module, you will be able to: • Use architecture wizard to parameterize a DCM • Instantiate the DCM into the design using the language template • Specify pin constraints using PACE • Download and test the design in hardware

General Flow • Step 1: Use the architecture wizard to configure a DCM • Step 2: Instantiate the DCM into a VHDL/Verilog design • Step 3: Use PACE to assign pin locations • Step 4: Verify PAD report and start a hyperterminal session • Step 5: Download the Design • Step 6: Operating the Real-Time UART clock

UART Real-Time Clock • The design understands some simple ASCII commands • TIME – current time displayed according to 24 hour clock in format hh:mm:ss • TIME hh:mm:ss – allows time to be set according to 24 hour clock • ALARM – current alarm time will be displayed according to 24 hour clock. The current status of the alarm will be displayed (ON, OFF, Active) • ALARM hh:mm:ss – allows the alarm to be set according to the 24 hour clock. The new alarm time and current status will be displayed. • ALARM ON – Enables the alarm to be active. Current alarm time and status will be displayed. • ALARM OFF – Disables the alarm. Current alarm time and status will be displayed

PicoBlaze Hardware Design Baud Count en_16_x_baud rx_data out_port[7:0] alarm D Q en uart_rx PicoBlaze D Q en rx port_id[7:0] interrupt 000 port_id[0] rx_data write_strobe rx_full Interrupt_ack rx_half_full Instructions tx_full, tx_half_full uart_tx tx port_id[0] Address Instructions Interrupt_event control You will add the DCM to the design DCM 50 MHz 100 MHz clk

Basic Overview of Source Input port definition For PicoBlaze Output port definition For PicoBlaze Register Names

Basic Overview of Source Checks to see if “TIME” Is entered correctly; Also Checks to see if a command Was entered Initialization Current time entered by user is tested, stored in PicoBlaze registers, and Transmitted to the UART for display On hyperterminal Prompt user for input, Checking for “TIME” Or “ALARM”

Basic Overview of Source Checks to see if “ALARM” Is entered correctly; Also Checks to see if a command Is entered Alarm time command entered by user is tested. If an alarm time is entered, it is stored in PicoBlaze registers, and Transmitted to the UART for display on hyperterminal