スピル制御試験計画

スピル制御試験計画. 2007 年 5 月 23 日 ハドロンビームライン SubGr. 清道明男. アウトライン スピル制御 DSP ボード製作・動作試験 HIMAC ビーム試験. スピル制御関係の工程. H19 年度:準備・設計 スピルシミュレーション EQ ・ RQ 磁石、電源設計 DSP ボード製作、動作試験 HIMAC におけるスピル制御ビーム試験 H20 年度:装置製作 EQ, RQ, フィードバック装置製作 H21 年度:インストール Q 磁石インストール:7月 スピルシステムオフビームコミッショニング:9月

スピル制御試験計画

E N D

Presentation Transcript

スピル制御試験計画 2007年5月23日 ハドロンビームラインSubGr. 清道明男 アウトライン スピル制御 DSPボード製作・動作試験 HIMACビーム試験

スピル制御関係の工程 H19年度:準備・設計 スピルシミュレーション EQ・RQ磁石、電源設計 DSPボード製作、動作試験 HIMAC におけるスピル制御ビーム試験 H20年度:装置製作 EQ, RQ,フィードバック装置製作 H21年度:インストール Q磁石インストール:7月 スピルシステムオフビームコミッショニング:9月 スピルフィードバックビームコミッショニング開始:10月 遅い取り出し開始:H20年12月、スピル制御ビーム:H21年10月 Akio Kiyomichi

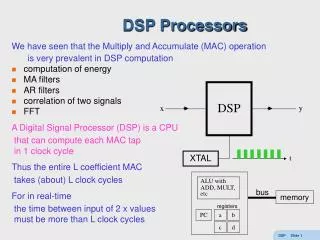

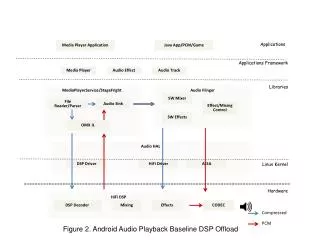

フィードバック装置の構成 開発項目 DSPプログラム 入出力部:デジタルI/O、AD変換 EPICSによる遠隔操作:モニタ、パラメータ変更など。 武蔵工大 加速器 電流パターン 開発範囲 Timing 取り出しゲート MR フィードバック装置 DSP (TI TMS320C6713) EQ O/E E/O D D/A モニタ DIGITAL A/D ビーム強度 D RQ D/A E/O O/E スピルモニタ スピル情報 A/D DIGITAL DIGITAL EPICS-IOC (SZ130-SIL) ハドロンG GP-IO : AD9235 KEK オンラインG開発 LAN 中央制御棟より操作 Akio Kiyomichi

武蔵工大の開発環境 Mark-1: 学生試作機[完成] DSPスタータキットで構成 Mark-2: 開発中、Mark-1の改良版 Mark-1に通信用I/Oボード(SZ130-SIL )を追加、EPICS-IOC開発 AD/DAボードの改良ORS-112 Mark-3: J-PARC用 オリジナル品、専用ボードの開発 中身はMark-2と同等 AD/DA 変換ボード A/D D/A Mark-2 通信ボード Ethernet FPGA (PSD, Memory) Linux (EPICS) FPGA EPICS 制御 LAN DSP (TI TMS320C6713) DSPコントロール Akio Kiyomichi

スピル制御用フィードバック装置の開発 昨年度までにできていること • Mark-1 完成、DSP部の単体動作 • ダミーデータ(PS, HIMAC)に対するフィードバック これから開発するべきこと • フィードバック装置の入出力部の開発 • デジタルI/Oを基本とする • 入力:オンラインG開発のADCボードを用いたI/O、加速器情報 • 出力:EQ,RQの電源設計と並行して形式を定める • 遠隔操作用通信部の開発 • LAN接続、EPICS-IOCの導入 • 受け渡し変数の取り決め、DSPプログラムの改造 • 遠隔操作アプリの開発 5 Akio Kiyomichi

放射線医学総合研究所での実験 • J-PARCと同じ1/3共鳴の遅い取り出しビームラインを利用したフィードバック装置の試験 実験計画 • HIMAC遅い取り出しの基礎データ収集 [H19年7月頃] 加速器操作無し、早期に実施する。現地調査含む • 線形 tune ramp に対するスピル構造を測定 • Linear ramp の場合、スピル構造にビーム分布が直に反映 • スピルをフラットにするための tune ramp が導ける • 疑似信号の元データとする • Mark-1 の動作試験。フィードバック出力の検証。 • HIMAC遅い取り出しのフィードバック試験 [H19年10月以降] Mark-2 完成後、加速器操作も行う。ビームタイム交渉の必要 • Mark-2 の動作試験 • 取り出し電磁石へのフィードバック • 機器(Mark-3,AD/DAボード等)の試験も行いたい • 実機試験の検討 Akio Kiyomichi

今年度の予定 H19年度前半 • Mark-2相当をKEKにて構築 • DSP開発の習得。アナログI/Oによるフィードバック試験 • 既存のDSPプログラムの検証・開発 • デジタルI/O部のR&D • 使用予定のAD/DAボードの接続試験 • 通信部のR&D、方針決定 • SUZAKU+EPICS-IOCで可能か、別の方法を考える必要があるか • HIMACの基礎データをおさえる 加速器デザインレビュー 9月頃 H19年度後半 • HIMACのビームを用いたフィードバック試験 • 遠隔操作に合わせたDSPプログラムの開発 • EQ,RQ 電源への入力信号の仕様決定 Akio Kiyomichi

中期展望 H19年度 EQ,RQ 電磁石・電源設計 • 入出力部の仕様決定。電源設計に反映させる。 H20年度 EQ,RQ 電磁石・電源製作 • 遠隔操作(EPICS)アプリの開発 • HIMACでMark-3、AD/DA、EPICSアプリまで含めた総合試験 12月 遅い取り出し開始 • フィードバック装置完成 • EQ,RQ 電磁石完成後、総合接続試験 H21年度 秋 遅い取り出しスピル制御ビーム開始 その他・検討事項 • シミュレーションとの組合せなどは可能か? • 計算出力を疑似信号として入力、Virtual Accelerator のようなもの Akio Kiyomichi

予備 9 Akio Kiyomichi

スピル制御 EQ(取り出し4極電磁石)1台 鋼板 ビームの整形、100Hz以下のノイズ除去 EQの磁場を変える=Tuneを変える Spill Height = Intensity/Time となるように電流パターン(ΔIEQ)を調整 RQ(リップル星4極電磁石)1〜2台 空芯 or フェライト 100Hz以上の高周波成分ノイズ除去 フィードバック回路 DSPによるデジタルフィードバック装置 HD真空遮蔽膜に設置のロスモニタよりスピル信号を受けて、EQ,RQの電流パターンを変更 EPICSによる遠隔操作 Spill Height = Intensity/Time Intensity Spill Time IEQ Akio Kiyomichi

Mark-Ⅱ システム構成 ① DSPボードTMS320C6713 DSK (TI社) DSP C6713(TI社) スターター・キット ② AD/DA ボードORS-112 入力 4ch:ADC 16bit x 4 出力 4ch:DAC 16bit x 4 100万ゲートのFPGA VartexⅡ1000-4C つき ③ 通信用IO ボードSZ130-SIL SUZAKU-S スターターキット イーサネット用I/O(選定中) ハード サンプリング周波数:225MHz FPGA内でPSD処理 DSP内で制御信号処理 ソフト C、 CCS、ISE、EPICS、 μCLinux 既成品、比較的早期に実験 構成 C6713+FPGA既成品

ADC DAC FPGA (PSD, Memory) FPGA (CPU) Ethernet DSP ② Mark-Ⅱ システム構成 右図参照 ハード 入力 アナログ:4ch(16 bit )、 出力 アナログ:4ch(16 bit ) サンプリング周波数:225MHz FPGA内でPSD処理 DSP内で制御信号処理 ソフト C言語、CCS、ISE、EPICS μCLinux 2.6 ③ ① 注:ボード上のメモリは省略

Mark-Ⅱ 概要 高性能32ビット浮動小数点DSP搭載 Xilinx SPARTAN 3 FPGA搭載 CPU TMS320C6713 プロセッサの最高性能 2400 MIPS , 1350 MFLOPS クロック周波数 225 MHz RAMのタイプと容量 8 MバイトSDRAM ブート用フラッシュメモリー 0.5 Mバイト ソフト C、CCS(Cコンパイラ、アセンブラ、リンカ) ① TMS320C6713 DSK

Mark-Ⅱ 入力 4ch 16 bit [AD9260 x 4] , Up to 2.5 MSPS 4Vpp, 200 Ohm inputs AC or DC coupled inputs 出力 4ch 16 bit [LTC2602 (2ch 内蔵) x 2] Up to 625kSPS/ch FPGA VartexⅡ1000-4C パワースペクトル(PSD)を実時間処理 内部にメモリを確保 ② AD/DA ボード ORS-112

Mark-Ⅱ FPGAの中にCPUコアを搭載 FPGA :XC3S1200E-4FG320C CPUコア:MicroBlaze DRAM : 16MB x 2 フラッシュメモリ: 8MB (SPI) LAN : 100 BASE-TX / 10 BASE-T OS: μCLinux 2.6 ③ 通信用IO ボードSUZAKUSZ130-SIL

Mark-Ⅱ 信号処理の開発手順 [市川、持木]

Mark-Ⅲ システム構成 マザーボード ドーターボード1(DSPC6713) ドーターボード2(FPGA SPARTAN3) メモリ(RAM、SIMM) I/Oボード(イーサネット、パラレルtoPC) ハード 入力 アナログ:4ch(16 bit )、 デジタル:4 ch 出力 アナログ:4ch(16 bit ) サンプリング周波数: max 1 Msps イーサネット( SUZAKU SZ130-SIL) ソフト C言語、CCS オリジナル品、専用

DAC FPGA ADC DSP Ethernet SIMM Mark-Ⅲ システム構成 ①マザーボード ②ADCボード コネクタ接続 ③DACボード コネクタ接続 ④ドーターボード1(DSPC6713) コネクタ接続 ⑤ドーターボード2(FPGA SPARTAN3) コネクタ接続 ⑥メモリ(RAM、SIMM) 一部ソケット接続 ⑦I/Oボード(イーサネット、パラレルtoPC)コネクタ接続 オリジナル品、専用 ① ③ ④ ② ⑦ ⑤ ⑥