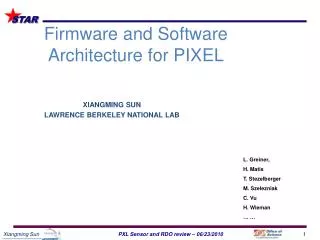

Firmware and Software Architecture for PIXEL

270 likes | 378 Views

XIANGMING SUN LAWRENCE BERKELEY NATIONAL LAB. Firmware and Software Architecture for PIXEL. L. Greiner, H. Matis T. Stezelberger M. Szelezniak C. Vu H. Wieman … …. Outline. R equirements for e vent readout mode Event readout mode Other firmware functions

Firmware and Software Architecture for PIXEL

E N D

Presentation Transcript

XIANGMING SUN LAWRENCE BERKELEY NATIONAL LAB Firmware and Software Architecture for PIXEL L. Greiner, H. Matis T. Stezelberger M. Szelezniak C. Vu H. Wieman … …

Outline Requirements for event readout mode Event readout mode Other firmware functions Firmware and readout software structure Summary

Test set • Individual sensor test - • A single sensor is connected. • Probe test - • The sensors are put on probe station and the power supply is controlled. • Infrastructure Test Board (ITB) test - • 10 sensors are connected in parallel, long cablesare used. • Beam test - • 4 sensers are built into a telescope. The trigger is included. • Phase-2 sector test - • Morethan 1 sectoris connected. The trigger is included. • Final version - • 40 sensors are connected. Long cablesare used. The trigger is included. Firmware structure is designed to handle all these tests. The set of firmware modules for the various tests will be very similar with only minor task dependant differences.

Rrequirement for event readout mode requirement : mass terminition board 40 sensors per readout board( Each sensor has 2 LVDS pairs. 80 LVDS pairs in 160MHz). Sensor digitizes signal and records hit address in on-chip memory, then transfer hit address serially. Trigger is STARDAQ1000(about 1KHz). DAQ DDL assumed throughputis 80MB/son average. (DDL link rated for 200MB/sec). mother board xilinx V5 PRO SIU/DDL DAQ PC

Data is buffered in FPGA frame1 frame2 frame3 STAR and DAQ policy: 1 trigger per event DDL peak speed(2Gb/s) is lower than data generation peak speed(12.8Gb/s). TPC can buffer 8 triggers when DDL is not available. PIXEL should buffer ≥8 triggers Trigger time Event data

Event format For sector Header token 7 Trigger info header system status Data block For ladder1 temperature Firmware version Hardware ID Data block For ladder2 Block start Data length ……. 10 words reserved … Hit address Data block For ladder3 sensor ID is encoded in four unused bits Data block For ladder4 ender end token

Event mode Readout structure for one sector Ladder#1 Ladder#2 Ladder#3 Ladder#4 Event Builder #1 (head token added) Event Builder #2 Event Builder #3 Event Builder #4 (end token added) Event fifo SIU

Event Builder Sensor 1 circular buffer output2 output1 … 10 sensors Serial to parallel conv Serial to parallel conv Trigger time memory data memory start frame memory Builder state machine To event fifo

Serial to parallel converter Sensor 1 output2 output1 … 10 sensors Serial to parallel conv Serial to parallel conv Serial-to-parallel converter 1,convert 160MHz 1 bit data to 10MHz 16bit parallel data. 2, add sensor ID into the data. Data memory scans Serial-to-parallel converter one by one every 10 ns (100MHz). It starts from sensor 1 and returns to sensor 1 after reaching sensor 10. data memory From sensor1 From sensor2 From sensor… From sensor10 From sensor… From sensor1 From sensor3

Circular buffers trigger token and buffer full Trigger time memory data memory frame counter when trigger comes frame1 frame2 index of start frame memory 512 words index of data memory for the first frame start frame memory index of data memory for the second frame 64K words 512 words

Data check out Trigger time memory get trigger time and start frame index data memory frame1 get buffer index for 2 frames frame2 Check out region where hit address bigger than trigger time for frame1 and smaller for frame2 Release unused memory. start frame memory

Buffering capability • 19K words/trigger (684kb).( buffer length in chip is assumed to be 500 words and 150 word for inner and outer ladder from simulation ) . Current FPGA has 3Mb for event mode. XC5VLX330 has 8Mb. • 256 continous triggers can be stored (data memory may be full already) • bottleneck is DDL. 39MB/s for trigger DAQ1000 In normal condition, memory and DDL usage 10 triggers can be buffered when the DDL link is busy.

Other firmware functions JTAG function (all sensors) Analog full frame readout (Mimostar3 and Phase1) Digital full frame readout (Phase1 and Ultimate) I2C device control (Phase1 and Ultimate) System monitoring (Phase1 and Ultimate)

Firmware structure 15 sensor System control can access every module DDL/USB PC

JTAG function (all sensors) sensor JTAG is used for initializing the sensor. JTAG is done by the FPGA in Virtex5 development board. We reserve 5 FPGA pins as JTAG pins which connect to sensor’s JTAG pin serially. The JTAG data is sent from PC to FPGA SRAM. The JTAG module in FPGA will read the data from FPGA SRAM and transmit the data to sensor by JTAG pins.

Analog full frame readout sensor analog signal is digitized in ADC ADS5272 ADS5272 300MHz, IOdelay is used data is buffered in SRAM

IO delay for digital data alignment Digital signals pass 7 meters before arriving FPGA. How the digital signals from all sensors are aligned? 1, set sensor to pattern mode, a single pulse is sent from sensor for each row. 2, scan IO delay setting from 0 to 63. readout data in event mode. 3, search for the pulse in data taken. plot the relation between pulse address and IO delay setting. 4, find the transition region in above plot. set IO delay by shifting a half clock. pulse 1 clock cycle N+1 N Scan steps 0 63 Transition region Iodelay set half clock

Digital full frame readout sensor

System monitoring We have a separate data channel to monitor the system in physics run. This channel includes a information builder module in FPGA, USB data channel and a monitor PC. If something wrong happens, we can easily see it from monitor PC. sensor

Readout software structure • Design Goal: • portable between Linux and Windows • every test can be scripted command: generate commands in windows and linux usb.exe :upload commands to FEE in windows download_data_block_to_FEE: upload commands to FEE in windows getdata:get frame data in windows and linux rorc_receive: get event data in linux IO delay package: tune IOdelay for each digital channel I2C package: control I2C device

System Control Hex file command usb.exe download_data_block_to_FEE 0x0402fffd 0x1d82ff3f 0x1502ffcf 0x2642ffff 0x2642fdff 0x2202feff 0x0c03fff0 0x1547ffff 0x1547ffff 0x1547ffff 0x1547ffdf 0x0cc7ffff 0x0cc7ffff …………. getdata rorc_receive Linux PC Windows PC

Summary The design meets the requirements as stated. The full set of expected operation modes are addressed.