Troubleshooting VME Bus Errors and TMB Firmware Integrity Issues

This document outlines the troubleshooting steps for resolving a bus error on the VME crate controller (VCC) caused by misloaded firmware in the TMB. The VCC hangs during the first command due to Rule 2.35 requirements. The document details programming efforts for TMB mezzanine PROMs, verifying firmware integrity through bit-by-bit comparisons using CERN software, and checking FPGA loading through a hard reset. Additionally, it discusses configurations and rate monitoring for CLCT layer triggers, along with firmware updates for ALCT and TMB systems.

Troubleshooting VME Bus Errors and TMB Firmware Integrity Issues

E N D

Presentation Transcript

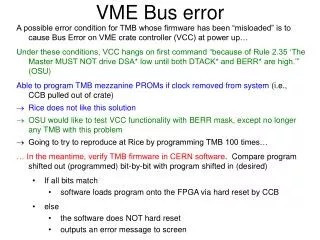

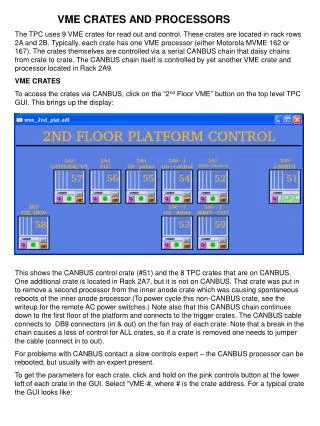

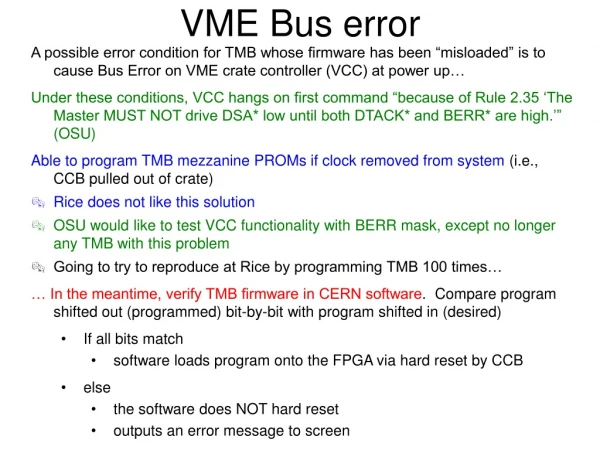

VME Bus error A possible error condition for TMB whose firmware has been “misloaded” is to cause Bus Error on VME crate controller (VCC) at power up… Under these conditions, VCC hangs on first command “because of Rule 2.35 ‘The Master MUST NOT drive DSA* low until both DTACK* and BERR* are high.’” (OSU) Able to program TMB mezzanine PROMs if clock removed from system (i.e., CCB pulled out of crate) • Rice does not like this solution • OSU would like to test VCC functionality with BERR mask, except no longer any TMB with this problem • Going to try to reproduce at Rice by programming TMB 100 times… … In the meantime, verify TMB firmware in CERN software. Compare program shifted out (programmed) bit-by-bit with program shifted in (desired) • If all bits match • software loads program onto the FPGA via hard reset by CCB • else • the software does NOT hard reset • outputs an error message to screen

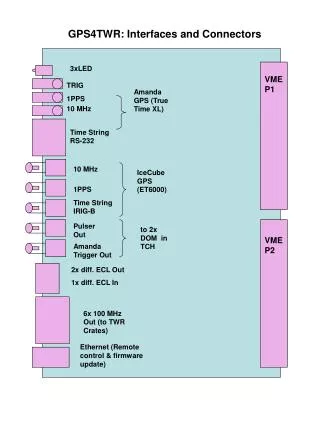

Going to define address XSIR -> 38 bits, TDI value = 0x3febffffff XRUNTEST -> 2 uSec XSDRSIZE -> 20 bits XTDOMASK -> 20 bits, mask = 0x000000 XSDRTDO -> 20 bits, TDI value = 0x000800 XSDRTDO -> 20 bits, TDO expected = 0x000000 XRUNTEST -> 14001 uSec XSIR -> 38 bits, TDI value = 0x3feaffffff XRUNTEST -> 0 uSec XSIR -> 38 bits, TDI value = 0x3fedffffff XRUNTEST -> 2 uSec XSDRSIZE -> 4100 bits XTDOMASK -> 4100 bits, mask = 0x000000000000000000000000000000000000000000… XSDRTDO -> 4100 bits, TDI value = 0x0000000000030c00006180000c30006102000c21c0… XSDRTDO -> 4100 bits, TDO expected = 0x000000000000000000000000000000000000000000… Address }Here comes program Request to shift out program XSIR -> 38 bits, TDI value = 0x3fefffffff XSDRSIZE -> 8196 bits XTDOMASK -> 8196 bits, mask = 0x07ffffffffffffffffffffffffffffffffffffffff… XSDRTDO -> 8196 bits, TDI value = 0x000000000000000000000000000000000000000000… XSDRTDO -> 8196 bits, TDO expected = 0x0000000000030c00006180000c30006102000c21c0… TMB firmware verify through bootstrap register (JTAG) Snippet from logfile of processing .xsvf file (written from original .mcs files with Impact): If “verify” option is selected when writing .xsvf file, the following commands take place for each address (after the prom has been written with above commands): In program, require: (TDO read-out & mask) = (TDO expected & mask) for every bit

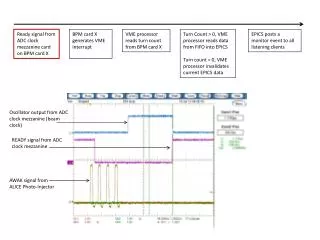

CLCT layer trigger 07/10/2007 TMB firmware. Configuration used: • clct_pretrig_enable = 1 • since it is a “pattern trigger” • layer_trig_enable = 1 • layer_trig_thresh = 2 • 2 comparator layers above threshold in any 1 bx • clct_halfstrip_pretrig_thresh = 7 • disable normal CLCTs • clct_pattern_thresh = 1 • allow layer trigger decision to happen in single bx N.B. layer trigger ~ 0.2-0.3bx faster than “normal” CLCT pattern trigger… (don’t know why?)

TMB counters with CLCT layer trigger • Quick notes: • match trigger rate ALCT trigger rate • Total rate ~1300Hz, may go to 2600Hz w/ALCT layer trigger? (N.B. “normal” coincidence rate 300Hz) • invalid pattern after drift 0

To do: • n-layer trigger • Does rate change with layer_trig_thresh? • ALCT (needs firmware download) • ALCT * CLCT • Synchronize CSC by pulsing • update CMS software with: • VME registers with respect to latest TMB firmware updates • broadcast ALCT firmware broadcast TMB firmware now disabled • Request to resurrect ALCT “Fast self-test” (?) • Write talk for TWEPP-07