제 8 장 . RISC 및 슈퍼스칼라 프로세서

제 8 장 . RISC 및 슈퍼스칼라 프로세서. 8.1 RISC 의 출현 동기 8.2 RISC 의 발전 경위 8.3 RISC 설계의 기본 원리 8.4 레지스터 세트의 설계 8.5 상용 RISC 들의 구조 8.6 슈퍼스칼라 프로세서. CISC / RISC. 스텐포드 대학 및 버클리 대학의 연구팀의 용어 정의 CISC(Complex Instruction Set computer) 프로세서 복합 명령어세트 컴퓨터 복합적인 연산들을 처리하는 명령어들을 가진 기존의 프로세서

제 8 장 . RISC 및 슈퍼스칼라 프로세서

E N D

Presentation Transcript

제8장. RISC 및 슈퍼스칼라 프로세서 8.1 RISC의 출현 동기 8.2 RISC의 발전 경위 8.3 RISC 설계의 기본 원리 8.4 레지스터 세트의 설계 8.5 상용 RISC들의 구조 8.6 슈퍼스칼라 프로세서

CISC / RISC • 스텐포드 대학 및 버클리 대학의 연구팀의 용어 정의 • CISC(Complex Instruction Set computer) 프로세서 • 복합 명령어세트 컴퓨터 • 복합적인 연산들을 처리하는 명령어들을 가진 기존의 프로세서 • RISC(Reduced Instruction Set computer) 프로세서 • 축소 명령어세트 컴퓨터 • CISC의 한계성을 극복하고자 제안한 새로운 프로세서 구조의 프로세서 • 간략화된 소수의 명령어들만 지원 Parallel Computer Architecture

RISC 프로세서의 출현 동기 • CISC의 문제점 • 명령어 비트 수가 길어져서 기억장치로부터 읽어오는데 여러 번의 인출 필요 • 다양한 종류와 길이의 명령어를 해독하기 위한 제어 유니트의 내부 회로 복잡도 증가 • 명령어 해독 및 실행 시간 증가 • 해결책을 위한 조사 • 명령어들의 사용 빈도 조사 • 사용 빈도가 낮은 명령어 제거 • 사용 빈도가 높은 명령어들을 단순화시키고 실행 과정을 H/W로 처리함으로써 명령어 실행의 고속화 시도 • 지역 변수 및 프로시듀어 매개변수의 수 조사 ①번의 결과로 확보되는 공간에 내부 레지스터들을 추가하여 주기억장치 액세스 수 감소 Parallel Computer Architecture

일반적인 프로그램들의 특성 • 프로그램 특성의 분석 결과 Parallel Computer Architecture

일반적인 프로그램들의 특성 (계속) • Assign문의 항들의 수에 대한 분포[%] • 프로시저 당 지역 변수들의 수에 대한 분포[%] • 프로시저 호출 당 전송되는 매개 변수들의 수에 대한 분포[%] Parallel Computer Architecture

RISC의 기본 설계 개념 • 각 명령어는 한 사이클(cycle) 내에 실행되도록 한다 • 명령어 수를 최소화 한다 (100개 이내, 최대 150개) • 명령어의 해독은 하드웨어로 처리한다 • 명령어 해독을 단순화시키기 위하여 명령어 형식을 고정시킨다 • 주소지정 방식의 종류는 1개 또는 2개로 하며, 최대 4개까지만 허용한다 • 연산의 동시성을 높이기 위해 데이터 통로(data path)를 파이프라인 구조로 한다 • 가능한 많은 수의 레지스터들을 가지도록 한다 • 기억장치 액세스는 간단한 명령어 구조를 가진 LOAD/STORE 명령어에 의해서만 이루어지도록 한다. 그 이외의 모든 데이터 이동 동작들은 내부 레지스터들 사이에서만 일어나도록 한다 • 계층 구조의 기억장치를 사용한다 Parallel Computer Architecture

RISC 프로세서의 발전 경위 • IBM 801 프로세서 : 1975년 개발 완료, 1982년 공개 • 평균 명령어 실행시간 = 1.1 사이클 • RISC I, II : 1981년, Berkeley 대학의 Patterson 교수와 Sequin 교수에 의해 실험적으로 설계 SPUR(Symbolic Processing Using RISCs) 및 SOAR(Small-talk On A RISC) 프로세서 개발로 이어짐 Sun SPARC(Scalable Processor ARChitecture) 프로세서 로 상용화됨 Parallel Computer Architecture

RISC 프로세서의 발전 경위 (계속) • MIPS 프로세서: 1983년, 스탠포드 대학의 Hennessy 교수팀에 의해 개발 MIPS-X, MIPS-X-MP 프로세서로 발전 • on-chip 명령어 캐쉬 탑재 • 예측 분기(squashed branch) 방식 도입 • MIPS R2000, R3000, R4000, R10000 프로세서로 상용화됨 • Clipper(Fairchild), AM29000 (AMD), MC88000 (Motorola)등 • 1980년대 중반 개발됨 • 산술 계산 속도를 높이기 위한 특수 기능 블록의 추가 • 명령어 선인출(instruction prefetch) 기능 추가 • 분기 처리를 위한 분기 목표 캐쉬(branch target cache)의 구현 • 가상 기억장치를 지원하는 기억장치 관리 기능의 강화 Parallel Computer Architecture

초기 CISC/RISC 프로세서의 비교 Parallel Computer Architecture

8.3 RISC 설계의 기본 원리 1)복잡한 명령어의 제거: 복잡하고 긴 시간이 걸리는 연산을 포함하는 명령어 제외 간단한 명령어들을 여러 개 반복 사용 [예] DIV 명령어 shift, add, sub 명령어들로 대치 2)주기억장치 액세스 명령어의 제한 • 데이터 연산 명령어 실행에 필요한 데이터는 항상 내부 레지스터에 저장 데이터 연산 명령어의 기억장치 액세스 불허 • 기억장치 액세스는 지정된 명령어들(LOAD, STORE)만 가능 • 레지스터 주소지정 방식을 사용하므로 명령어 코드의 비트 수 감소 • 유효 주소(effective address) 계산 시간이 절약 Parallel Computer Architecture

LOAD/STORE 명령어의 종류 Parallel Computer Architecture

RISC 설계의 기본 원리 (계속) 3)주소지정 방식의 단순화 • 유효주소 계산 시간을 줄이기 위하여 주소지정 방식 종류 최소화 [예] RISC I의 명령어 형식 • C : 명령어 실행 결과에 따라 조건 코드 세트 여부 지정 • DEST : 목적지 레지스터 번호 • SRC : 근원지 레지스터 번호 • I = 1 : OFFSET = 데이터 immediate addressing modeI = 0 : OFFSET = 레지스터 번호 register addressing mode Parallel Computer Architecture

RISC 설계의 기본 원리 (계속) 4) 파이프라이닝 • 명령어 인출, 해독, 실행 유니트, 기억장치 액세스 등을 파이프라인으로 구성 [문제점] LOAD 및 STORE 명령어의 실행 단계가 최소 두 단계 소모 LOAD X, R0 ; M[X] R0 ADD R0, R1 ; R0+R1 R1 Parallel Computer Architecture

RISC 설계의 기본 원리 (계속) [해결책] • H/W Interlocking • LOAD/STORE 명령어 실행 후, 자동적으로 NO-OP 명령어 코드에 해당하는 지연 슬롯(delay slot) 삽입 • 프로그램 실행 순서의 재조정 • 컴파일러가 프로그램 코드를 조사하여 LOAD/STORE 명령어 실행과 무관한 명령어를 재배치하는 방법 불가능 시 지연 슬롯 삽입 • MIPS 프로세서의 재구성기(reorganizer) : 컴파일러의 부담을 줄이기 위하여 명령어의 실행 순서의 재조정을 담당하는 별도의 프로그램 Parallel Computer Architecture

RISC 설계의 기본 원리 (계속) 5) 마이크로프로그램의 제거 • 명령어들이 단순화됨으로써, 하드웨어만으로 명령어 해독 가능 • 명령어 인출 유니트에 의하여 인출된 명령어 코드의 각 비트들이 그 명령어 실행에 필요한 제어 신호들을 발생시키는데 직접 사용 RISC 프로세서의 고속화 • 제어 유니트 내의 제어 기억장치(control memory) 제거 공간 여유 6) 고정된 명령어 형식 • 하드웨어에 의한 명령어 해독 및 실행을 위해서는 고정된 명령어 형식이 필요 Parallel Computer Architecture

8.4 레지스터 세트의 설계 • RISC 설계 원리를 적용한 결과 • 프로세서 내부에 공간적 여유 발생 내부 기억장치(레지스터)증가 가능 • LOAD나 STORE 명령어의 실행 횟수 감소 데이터 액세스 시간 단축 • 중첩 레지스터 윈도우(Overlapping Register Window) 방식 • 증가된 레지스터들의 효율적 운용 목적 • RISC I 프로세서 (SPARC 프로세서)에서 도입 • 520개의 레지스터 • 공통변수들 및 전출입 매개변수들의 저장에 분할 사용 Parallel Computer Architecture

중첩 레지스터 윈도우 방식 • 전체 레지스터들을 여러 개의 그룹으로 분할 • 각 프로시저(procedure)가 한 그룹씩 사용 • 보이는 레지스터들(visible registers) • 현재 수행중인 프로시저가 사용할 수 있는 32개의 레지스터들 • 네 개의 소그룹들로 나누어져 사용 • 공통 변수(global variables) 그룹 : 8개 • 전입 매개변수(incoming parameters) 그룹 : 8개 • 지역 변수(local variables) 그룹 : 8개 • 전출 매개변수(outgoing parameters) 그룹 : 8개 Parallel Computer Architecture

중첩 레지스터 윈도우 방식 (계속) • 한 그룹의 ‘보이는 레지스터들’이 네 개의 소그룹들로 나누어진 모습 Parallel Computer Architecture

중첩 레지스터 윈도우 방식에서 전체 레지스터의 활용 원리 Parallel Computer Architecture

중첩 레지스터 윈도우 방식 (계속) • CWP(Current Window Pointer) • 현재 사용중인 윈도우의 첫번째 레지스터를 가리키는 포인터 • 프로시저가 호출될 때마다 (24가 아닌) 16씩 증가 • Calling procedure의 전출 매개변수 그룹과 called procedure의 전입 매개변수 그룹이 중첩(overlap) Overlapping register window라고 불림 Parallel Computer Architecture

중첩 레지스터 윈도우 방식 (계속) [예] 전체 레지스터 수가 520개인 경우에 몇 개의 프로시듀어들이 연속적으로 호출될 수 있는가? • 512 / 16 = 32개 : 호출의 깊이(calling depth) • 32개 이상의 프로시듀어들이 호출되는 경우에는 ? • 전체 레지스터 세트가 순환 버퍼(circular buffer)를 형성 • 트랩(trap) 발생 첫 번째 프로시저에 대한 정보는 기억장치 내 스택에 저장 • 33번째 프로시저 정보를 첫 번째 레지스터 윈도우에 저장 • 그 이상의 호출 시, 위의 과정 반복 • 프로시저 호출이 연속적으로 32번 이상 일어나는 프로그램은 거의 없음 Parallel Computer Architecture

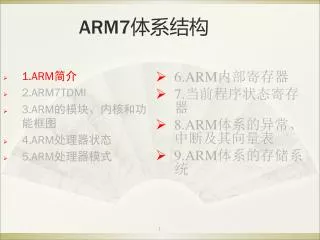

8.5 상용 RISC 프로세서들의 구조 8.5.1 SPARC 프로세서 • 1987년, Sun Microsystems사에 의해 개발 • 공개형 프로세서 구조(open processor architecture) • SPARC는 제조가 완료된 프로세서 칩에 대한 명칭이 아니라,새로운 RISC형 프로세서 구조에 대한 정의 • 동일한 구조에 대하여 서로 다른 방법(반도체 제조 기술 등)으로 구현 가능 • 동일한 구조에 대하여 제조 기술에 의한 경쟁을 유도 • 더 빠른 프로세서 제조 가능 (5개사 이상의 회사가 제조 참여) • 가상 캐쉬(virtual cache) 사용 : 캐쉬의 주소가 프로세서에 의해 발생된 가상 주소를 그대로 사용 [비교] 일반적으로 캐쉬의 주소는 MMU에 의해 변환된 물리적 주소 사용 캐쉬 액세스 시간에 주소변환 시간이 포함되어 길어짐 Parallel Computer Architecture

SPARC프로세서의 내부 구성도 Parallel Computer Architecture

SPARC 프로세서 (계속) • 32비트 프로세서 • 단어의 길이, 주소의 비트 수 : 32비트 • 명령어 길이, 레지스터 폭 : 32비트(고정) • 기억장치 단어 정렬방식 : big-endian 방식 [비교] 80X86 마이크로 프로세서 : little –endian 방식 Parallel Computer Architecture

SPARC 프로세서 (계속) • 명령어 실행 과정 : 4단계 파이프라인 • 레지스터 세트 • 중첩 레지스터 윈도우 방식 • 최대 520개 = (32x16)+8 • 공통 레지스터들 중의 첫번째 레지스터인 R0 =0으로 고정 Parallel Computer Architecture

SPARC 명령어 세트 • 산술 및 논리 연산 명령어의 형식 Parallel Computer Architecture

SPARC 명령어 세트 (계속) • SETHI 명령어 • 즉치 데이터(immediate data)필드가 주소로 사용될 경우, 길이가 13비트이므로 전체 기억장치의 주소 공간 액세스 불가능 SETHI 명령어 사용 • 즉치 데이터 필드의 22비트를 DEST 필드가 지정하는 공통 레지스터의 상위 22비트 값으로 세트하고, 하위 10비트는 0으로 세트 • 이어서 LOAD/STORE 명령어가 실행되면, 즉치 데이터 비트들이 그 레지스터의 하위 비트들과 더하여져서 32비트의 유효 주소를 생성 기억장치의 전체 주소 영역 액세스 가능 Parallel Computer Architecture

SPARC 명령어 세트 (계속) • 조건 분기 명령어 • 단어 단위로 지정하므로, 최대 16M 바이트 영역 내로 분기 가능 • A비트가 1이면, 분기가 발생할 경우에만 지연 슬롯 실행 • 호출 명령어 형식 • 단어 단위로 지정하므로, 최대 4G 바이트 영역내의 명령어 호출 가능 Parallel Computer Architecture

SPARC의 어셈블리 명령어들 Parallel Computer Architecture

SPARC의 어셈블리 명령어들 Parallel Computer Architecture

SPARC 어셈블리 프로그램 예 : ‘Towers of Hanoi’ Parallel Computer Architecture

SPARC 어셈블리 프로그램 예 : ‘Towers of Hanoi’ (계속) Parallel Computer Architecture

8.5.2 MIPS 프로세서 • SPARC와 같은 점 • 단어 길이 = 32 비트 • 명령어 길이 = 32 비트 • 기억장치 주소 공간 = 4 Gbytes(232) • 명령어 실행 과정의 파이프라이닝 • LOAD/STORE, JUMP 및 CALL 명령어에서 지연 슬롯 사용 • 바이트 단위의 주소 지정 가능 • FPU 및 보조 프로세서 지원 Parallel Computer Architecture

MIPS 프로세서 • SPARC와 다른 점 • 기억장치 저장 방식 : big-endian과 little-endian 중 하나로 선택 가능 • 레지스터 수 = 32개 • 프로시저 호출에 걸리는 시간이 SPARC에 비하여 길다 • 문맥 교환(context switching) 용이 • 절약되는 칩상의 공간에 MMU와 캐쉬 제어기 탑재 • 조건 코드가 별도로 지정되어 있지 않다 • 지연 슬롯 삽입 : H/W interlocking 방식 대신 컴파일러를 이용 • 명령어 파이프라인의 단계 수 = 5 Parallel Computer Architecture

MIPS의 명령어 파이프라인 Parallel Computer Architecture

MIPS 프로세서의 내부 구조 Parallel Computer Architecture

MIPS의 레지스터 세트 • 32개의 32비트 레지스터로 구성 • 중첩 레지스터 윈도우 방식의 단점 • 문맥 교환시, 현재 프로세스가 사용 중이던 레지스터 윈도우의 모든 정보들을 기억장치에 저장하고, 새로운 프로세스를 위한 정보들을 읽어오는데 긴 시간이 소요 • 각 그룹에 저장할 변수들의 수가 8개를 초과하는 경우에 곤란 • 많은 수의 레지스터가 필요하기 때문에 칩상의 면적을 크게 차지 Parallel Computer Architecture

MIPS의 레지스터 세트 Parallel Computer Architecture

MIPS의 명령어 세트 • 분기 목적지의 주소 계산 • (PC의 최상위 4비트) + ((JUMP TARGET ADDRESS) << 2) • Superpage : PC의 최상위 4비트로 구분 각 256M(228) • Superpage 사이의 분기 불가능 (0x0ffffffc 0x10000004) Parallel Computer Architecture

8.6 슈퍼스칼라 프로세서 8.6.1 명령어-수준 병렬성 • 명령어-수준 병렬성(Instruction-level parallelism) : 명령어들이 서로 독립적이어서 동시에 실행될 수 있는 상태 • 하드웨어 병렬성(H/W parallelism, machine parallelism) : 실제 명령어들을 병렬로 실행하는 데 사용될 수 있는 하드웨어 능력 [예] 어떤 프로세서가 두 개의 ALU들과 하나의 LOAD/STORE 유니트들을 가지고 있다면, 아래의 세 명령어들을 동시 실행 가능LOAD R1, A ADD R2, R3 MUL R4, R5 Parallel Computer Architecture

하드웨어 자원의 이용률 저하 원인 • 명령어-수준 병렬성 및 하드웨어 병렬성이 존재하더라도, 아래의 이유 때문에 성능 향상에 한계가 있게 됨 • 데이터 의존성(data dependency) • 흐름 의존성(flow dependency) • 반의존성(anti-dependency) • 출력 의존성(output dependency) • 자원 충돌(resource conflict) Parallel Computer Architecture

흐름 의존성 (flow dependency) • 어떤 명령어를 실행하기 위해서는 앞의 다른 명령어의 실행 결과를 이용해야 하는 상황 두 명령어는 반드시 순차적으로 실행되어야 함 [예] I1: LOAD R1, A ; R1 ← M[A] I2: SUB R1, R2 ; R1 ← R1 - R2 I3: MOV R3, R1 ; R3 ← R1 Parallel Computer Architecture

동적 실행(dynamic execution) • 프로그램에서 흐름 의존성이 존재하는 경우에, 뒤에 위치한 명령어들 중에서 현재 실행하려는 명령어와 의존성이 존재하지 않는 것이 있으면, 순서를 변경하여 먼저 실행하는 방법 • 펜티엄 프로(Pentium Pro) 프로세서 이후의 대부분 프로세서들에서 사용 Parallel Computer Architecture

반의존성(antidependency) • 흐름 의존성이 존재하지 않는 명령어들 간이라도, 동적 실행 과정에서 순서를 바꾸어 실행할 수는 없는 의존 관계 • 흐름 의존성과 반대 방향의 의존성 [예] I4: MUL R1, R2 ; R1 ← R1 × R2 I5: ADD R2, R4 ; R2 ← R2 + R4 Parallel Computer Architecture

출력 의존성(output dependency) • 두 명령어들의 실행 결과가 동일한 목적지에 저장되는 경우 [예] I6: SUB R1, R2 ; R1 ← R1 - R2 I7: MOV R3, R1 ; R3 ← R1 I8: MOV R1, #2 ; R1 ← 2 • I6 I7 : 동적 실행을 위하여 I6와 I8을 동시에 실행시키는 경우에는 I7이 잘못된 R1값을 이용할 위험이 존재 Parallel Computer Architecture

자원 충돌(resource conflict) • 동시에 실행될 수 있는 명령어들이 같은 H/W 자원을 사용하며, 그 수가 충분하지 못한 상황 • 자원의 예 : ALU, 기억장치 모듈, 캐쉬, 레지스터, 등 [예] I6: SUB R1, R2 ; R1 ← R1 - R2 I7: MOV R3, R1 ; R3 ← R1 I8: MOV R1, #2 ; R1 ← 2 • I6와 I8은 출력 의존성 뿐 아니라, 자원 충돌도 존재하므로, 동시 실행 불가능 레지스터 재명명(register renaming)으로 해결 가능 (8.6.3절) Parallel Computer Architecture

8.6.2 명령어 발송 정책 • 명령어 발송(instruction issue) : 프로세서가 독립적인 명령어들을 찾아서 명령어 실행 파이프라인으로 보내어 실행이 시작되도록 하는 과정 • 명령어 발송 정책(instruction issue policy) : 명령어를 발송하는 데 필요한 프로토콜 ‧순서대로 발송하고 순서대로 종료(in-order issue with in-order completion) ‧ 순서대로 발송하고 순서와 다르게 종료(in-order issue with out-of-order completion) ‧ 순서와 다르게 발송하고 순서와 다르게 종료(out-order issue with out-of-order completion) Parallel Computer Architecture

2-way 슈퍼스칼라 프로세서 내부 구조의 예 • 4-단계 파이프라인 • 인출 및 해독 단계 : 두 개의 별도 유니트들 & 미리보기 윈도우 • 실행 단계 : 네 개의 유니트들(곱셈기, 가산기, logic, loader) Parallel Computer Architecture

(1) 순서대로 발송하고 순서대로 종료하는 방식 • 가장 간단한 명령어 발송 정책 • 원래 프로그램 순서대로 발송하고, 결과들도 원래 순서대로 저장 • 실행 단계가 미리 종료된 명령어라도, 프로그램 순서 상으로 그 이전에 위치한 명령어가 완전히 종료되지 않았다면, 기다렸다가 순서에 맞추어 마지막 단계인 저장(S) 단계를 수행. Parallel Computer Architecture

프로그램 예 [예] I1: LOAD R1, X ; R1 ← M[X] I2: ADD R2, R1 ; R2 ← R2 + R1 I3: ADD R3, R4 ; R3 ← R3 + R4 I4: MUL R4, R5 ; R4 ← R4 × R5 I5: OR R6, #01 ; R6 ← R6 ∨ 01 I6: MUL R6, R7 ; R6 ← R6 × R7 o I1과 I2 사이에는 흐름 의존성이 존재한다 (I1 ―→ I2). o I3와 I4 사이에는 반의존성이 존재한다 (I3 ―+→ I4). o I5와 I6 사이에는 흐름 의존성과 출력 의존성이 존재한다 (I5 ―→ I6, I5 ―o→ I6) Parallel Computer Architecture