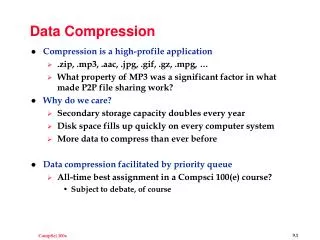

Data Compression Techniques for Optimizing Test Time in System-on-Chip Architectures

200 likes | 333 Views

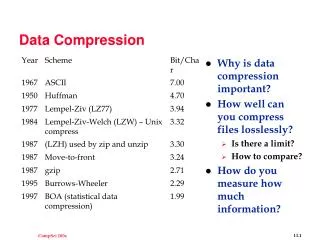

This paper explores innovative methods for data compression in system-level testing of multi-core SoCs. It highlights a compression approach that is independent of the circuit netlist and test data, allowing for optimized test time without specialized tools. The experimental results demonstrate a significant reduction in overall test time by exploring architectural solutions and optimizing core assignments. By adopting a new compression algorithm, the study reveals an available test parallelism increase of over 50%, while maintaining fault coverage during testing.

Data Compression Techniques for Optimizing Test Time in System-on-Chip Architectures

E N D

Presentation Transcript

Test Data Compressionand TAM Design J. Dalmasso, ML Flottes, B. Rouzeyre CNRS/ Univ. Montpellier II France

Introduction DUT DUT DUT ... ... 30 decompression 3 30 3 T1, W1 T2 = T1/10, W2 = 10xW1 T3 = T1/10, W3 = W1

Introduction DUT DUT DUT ... ... 30 decompression 3 30 3 T1, W1 T2 = T1/10, W2 = 10xW1 T3 ≥ T1/10, W3 = W1

Introduction N Scan Chains CLK XXXXX0XXXX1X FSM SR SR SR SR 0 0 Control Scan enable W ATE Channels • Compression method • independent of the circuit netlist • independent of the test data • no specific test tool is needed • No impact on fault coverage

Introduction N Scan Chains CLK FSM SR SR SR SR 0 0 Control Scan enable W ATE Channels • Compression method • independent of the circuit netlist • independent of the test data • no specific test tool is needed • No impact on fault coverage core test time may be affected

Outline • Compression at system level • Problem Statement (test time optimization) • Algorithm • Experimental Results

Compression at System level C1 C2 C3 WTam1 C4 C5 WTam2 Test Access Mechanism = Test bus 1500 ready cores Partitioned test buses

Compression at System level • Solution space C4 C2 C3 WTam1 WATE C1 C5 C1 C2 C3 WTam2 WTam1 WATE C4 C5 WTam2

Compression at System level • Solution space C4 C2 C3 C1 C2 C3 C1 C4 WATE1 WTam1 WTam1 WTam1 WATE WATE C1 C5 C4 C5 C2 WATE2 WTam2 WTam2 WTam2 C3 C5 WATE3 WTam3

ProblemStatement • Inputs • WATE channels, WTAM bit width • n Cores Ci • Problem • Determine optimal number of sub-buses • Determine compression ratio on every bus • Core assignment/scheduling for minimal test time • compression increases test parallelism but may increase individual test time

Algorithm Outer loop • For each ATE channel partition • For each compatible TAM partition • Find best core assignment (the lowest total test time) • If this assignment decreases global test time • memorize architecture and its associated scheduling

Algorithm Outer loop Inner loop • For each ATE channel partition • For each compatible TAM partition • Find best core assignment (the lowest total test time) • If this assignment decreases global test time • memorize architecture and its associated scheduling • Initial Solution • Put each core on the smallest possible bus • Compute test time • Improvement • Find bus Bi which has the longest test time • For each core on Bi, • For all other bus Bj ( j ≠ i ) • move core from Bi to Bj • Compute test time • Move core C from Bi to Bj so that test time is smallest

Core test time vs Compression Indentification: Test Time = ( / compression ratio) +

Core test time vs Compression Indentification: Test Time = ( / compression ratio) +

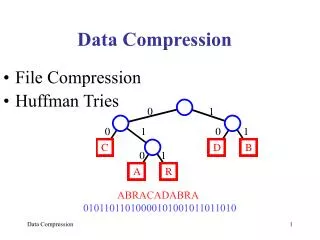

Experiment on a 16 cores SoC C1 C2 C3 C4 32 ATE C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 64 TAM

Experiment on a 16 cores SoC ATE=32 TAM=64 T3=57941 C1 C2 C3 C4 C8 5 6 C9 C10 C7 C6 5 12 C12 C5 C11 7 14 C16 C14 7 No Compression ATE=TAM=32 T2=127413 16 C15 C13 8 16 ATE=TAM=64 T1=55738

Conclusion • Data Compression for System testing • Test width reduction is the primary goal • higher test parallelism without ATE cost • Method for exploring architectural solutions • one compressor for all cores, one compressor per core, no compressor... • independant of the compression technique • Test time reduction > 50%