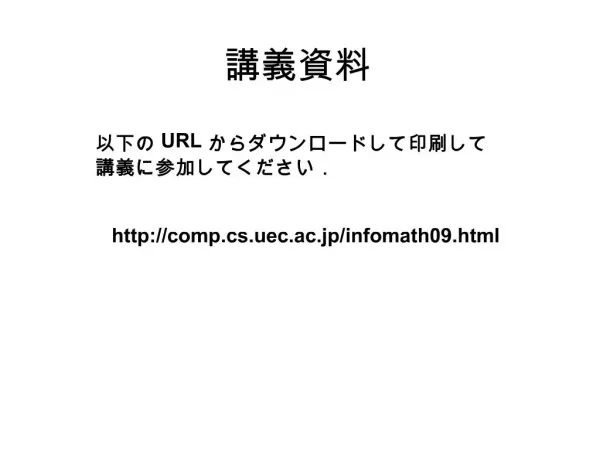

URL

Development of new technologies for accelerators and detectors for the Future Colliders in Particle Physics. URL. Working Plan for future Colliders. Off-detector and transfer electronics Module controller (UB) Design of this module is to be done closely with interconnection and data transfer.

URL

E N D

Presentation Transcript

Development of new technologies for accelerators and detectors for the Future Colliders in Particle Physics URL

Working Plan for future Colliders • Off-detector and transfer electronics • Module controller (UB) • Design of this module is to be done closely with interconnection and data transfer. • Interconnection and data transfer. • Data transfer rate from ASIC to module controller and finally to readout and off-detector electronics can be as high as 20GB/s if occupancy is high and data sparsifying is not possible [ILC-RDR2007]. • Physical connections: optical fiber or LVDS serialization. • Objective: reduce noise, cabling and connectors. • Study of EMC and signal integrity required. • Task is closely related to System Integration and Engineering. ILC Santiago 2008

Working Plan for future Colliders • Off-detector and transfer electronics • DAQ: • Design and test of a stand-alone portable setup. • Same setup for Lab and testbeam. • FPGA-based dedicated boards connected to PC for analysis. • VHDL FPGA firmware. • Acquisition and analysis software on PC. • Testbeam preparation: • Adaptation boards for signal format/level conversion. • Overcome limitations of available facilities. • Real-time data analysis to allow in-site test decisions to better profit from available beam characteristics. ILC Santiago 2008

Working Plan for future Colliders • DHP for Belle II • SEU protection for memory cells (Hamming correction or others…) • FPGAs -> URL • ASIC -> MPI (Andreas) • Interface DHP-DHH and DHH-back-end electronics • To be done in close contact with KEK (URL) • Gigabit TX (physical, coding, FEC…) • FPGAs -> URL • ASIC -> U.Bonn DHP Meeting UB 2008

Working Plan for future Colliders • Project Status: DEPFET officially approved for Belle II !!! • But geometry of beam pipe and cooling system not decided yet • Will affect number and size of modules • …which in turn will affect data rate • Must not make strong assumptions, find flexible solution that can be adapted to either outcome • E.g. serializing ratio, channel coding • Fortunately, we are in the FPGA part KEK Meeting 2008

Working Plan for future Colliders • Better understanding of mechanical issues, cooling. • But nothing fixed yet, number of pixels and readout time not decided data rate unknown. • Must be very flexible, foresee different options. Ringberg 2009

Current Status @URL • System level integration on Belle II @KEK • Physics and overall • Participation on meetings and following discussions • Radiation dose study • Will affect FPGA family selection, code selection, etc… • Testbeam @ CERN (July’2009 ?) • Willing to participate. • Great opportunity to connect to DEPFET people and take a global system picture. • But… very few manpower on our group.

Current Status @URL • Gigabit TX • First Tests on LVDS TX • Very FPGA dependent (Stratix w/o DPA, Stratix II ok, Stratix II+ GX version may be required). • Parameter tuning is critic: lots of things to be understood. 1 Gbps on Stratix II GX done

Current Status @URL • Gigabit TX • Development board acquisition • Transceiver Signal Integrity Development Kit, Stratix II GX Edition • Preparing lab setup for BER test (with perturbations) • Protocols • Serial RapidIO (up to 3.125Gbps) • Gigabit Ethernet • ...

Current Status @URL • SEU Protection & FEC codes • SEU Protection for memory cells • Hamming correction implementation cost on FPGAs • FPGA vendor and family comparison considering radiation dose, system performance, etc… (Altera, Actel, Xilinx…) • Coding and FEC cost and alternatives

Current Status @URL • System integration on FPGAs • NIOS II evaluation and setup • Useful on lab setups and prototyping • Firmware development • Defining collaboration with U.Giessen

Working Plan for future Colliders • Planning 2009 2010 2011 ILC Santiago 2008 Test setup • Lab setup • EMC • Digital links Interconnection and data transfer • PCB Design • VHDL firmware • Signal integrity • Test DAQ (study, HW development, SW) • Testbeam study • PCB Design • VHDL firmware • Analysis SW • Test