Switch-based Boolean computation

Switch-based Boolean computation. Shannon’s work : A Symbolic Analysis of Relay and Switching Circuits(1938). Two-terminal and four-terminal switches. A lattice of four-terminal switches. 3 × 3 2D switching network and its lattice form. Motivation. Regular arrays

Switch-based Boolean computation

E N D

Presentation Transcript

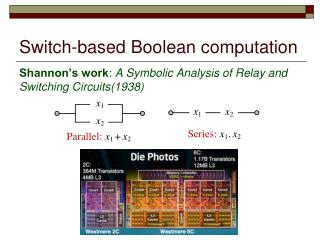

Switch-based Boolean computation Shannon’s work: A Symbolic Analysis of Relay and Switching Circuits(1938)

A lattice of four-terminal switches 3 × 3 2D switching network and its lattice form

Motivation Regular arrays Regularity; ease of design. Nanotechnology Self-assembled systems. Self-assembled circuit with 64,000 elements in three minutes Self-assembled nanowires

Motivation Crossbar array of four-terminal switches Technology independent Nanowire four-termial switch Spin-wave four-termial switch

Outline Logicsynthesis for lattices of four-terminal switches. Defect tolerance for lattices of four-terminal switches. Mathematics of lattice-based computation: self-duality problem. Future Work

Outline Logicsynthesis for lattices of four-terminal switches. Defect tolerance for lattices of four-terminal switches. Mathematics of lattice-based computation: self-duality problem. Future Work

Boolean functionality and paths Switches are controlled by Boolean literals. fLevaluates to1iff there exists a top-to-bottom path. gLevaluates to1iff there exists a left-to-right path.

Logic synthesis problem How can we implement a given target Boolean function fTwith a lattice of four-terminal switches? Example:fT= x1x2x3+x1x4

Logic synthesis problem Example:fT= x1x2x3+x1x4+x1x5 9 TOP-TO-BOTTOM PATHS!

Our synthesis method Example:fT= x1x2x3+x1x4+x1x5 fTD= (x1+x2+x3)(x1+x4)(x1+x5) fTD= x1 + x2x4x5 + x3x4x5 • Start with fTandits dual. • Assign each product of fT to a column. • Assign each product of fT D to a row. • Compute an intersection set for each site. • Arbitrarily select a literal from an intersection set and assign it to the corresponding site.

Math behind the method – Theorem 1 Theorem 1(Altun and Riedel, 2010): If fT and fTD are implemented as subsets of all top-to-bottom and left-to-right paths, respectively, thenfL=fTand gL=fTD.

Math behind the method – Theorem 1 Theorem 1 allows us to only consider column-paths.We do not need to enumerate all paths!

Math behind the method – Theorem 2 Lemma (Fredman and Khachiyan, 1996): Consider products Pi and PjoffT and fTD in ISOP forms, respectively. Pi ∩ Pj ≠ Ø Theorem 2 (Altun and Riedel, 2010):Consider a product Pi of fT in ISOP form. For any literal x of Pi there exists at least one product Pj of fTD such that Pi ∩ Pj = x.

Math behind the method – Theorem 2 Theorem 2 (Altun and Riedel, 2010):Consider a product Pi of fT in ISOP form. For any literal x of Pi there exists at least one product Pj of fTD such that Pi ∩ Pj = x. Each column is implements a product!

Our method’s performance The time complexity: O(m2n2) Size of the lattice:m×n n and m are the number of products of the target function fT and its dual fTD, respectively.

Implementing parity functions A Parity functionfevaluates to 1 iff the number of variables assigned to 1 is an odd number:

Implementing parity functions Lattice size: (logm +1)×n compared tom×n n and m are the number of products of the target function fT and its dual fTD, respectively.

A lower bound on the lattice size Circuit complexity Lower bound

Lower Bound • The lower bound is derived from two variables v and y. v:The maximum number of literals in a product of the target function fT in ISOP form. y:The maximum number of literals in a product of the target function’s dual fTD in ISOP form.

Deriving the lower bound vT1=3 vT2=3; yT1=3 yT2=2 yT1> yT2

Deriving the lower bound R and C are the numbers of rows and columns of the lattice that implements fT, respectively.

The lower bound numbers The lattice size R×Cfor differentvand yvalues