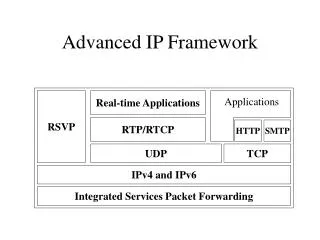

Advanced Porting The Framework

Advanced Porting The Framework. Intel Corporation Software and Services Group. Agenda. Create a New Platform Build Minimal porting job to run EFI Shell Platform specific porting features. New Platform Build. Create a New Project Directory.

Advanced Porting The Framework

E N D

Presentation Transcript

Advanced Porting The Framework Intel Corporation Software and Services Group

Agenda • Create a New Platform Build • Minimal porting job to run EFI Shell • Platform specific porting features

New Platform Build Create a New Project Directory • Identify the Platform that this Project is a part of, PROJECT_PLATFORM. Platforms are usually closely tied to a processor/north bridge/south bridge combination. • Choose a Project name, PROJECT_NAME. This is often defined in the PlatformTools.env. Currently we are describing Bearlake as an example project name. • Choose a Project family, PROJECT_FAMILY. This is often defined in the PlatformTools.env. • The Platform\PROJECT_FAMILY\ • PROJECT_PLATFORM directory to Platform\PROJECT_FAMILY \PROJECT_NAME. In the case of the Bearlakeexample platform, the source directory to copy is Platform\IntelDpg\PROJECT_PLATFORM.

The Framework Directory Tree8.x code base • Framework • Application • Bus • Chipset • Lakeport - MemoryInit • Blackford - MemoryInit • ESB2 • IntelIch - ICHX - SmBus • SMC • CPU • CSM • GUID • Include • Library • Platform • IntelDpg – Lakeport Pei – Dxe - Platform • IntelEsg – StarLake Pei – Dxe - Platform • IntelSSG • Lakeport - Build • Ppi • Protocol • Tools Bearlake ICHX Bearlake Bearlake

Agenda • Create a New Platform Build • Minimal porting job to run EFI Shell • Platform specific porting features • \$(PLATFORM_SOUTH_PATH) for LAKEPORT is \IntelDpg\Lakeport

PWR ON SEC PEI DXE BDS OS General Overview SECurity Pre-Efi Initialization Driver Xecution Environment Boot Device Selection

Device, Bus, or Service Driver Power on [ . . Platform initialization . . ] [ . . . . OS boot . . . . ] Shutdown Boot Flow Exposed PlatformInterface Pre Verifier OS-AbsentApp CPUInit Transient OS Environment verify Chipset Init Board Init Transient OS Boot Loader OS-PresentApp EFI Driver Dispatcher Boot Manager Intrinsic Services ? Final OS Environment Final OS Boot Loader security Security (SEC) Pre EFI Initialization (PEI) Driver Execution Environment (DXE) Boot Dev Select(BDS) Transient System Load (TSL) Run Time (RT) After Life (AL)

legacy Option ROMs legacy OS Loader legacy Option ROMs legacy OS Loader EFI OS Loader EFI OS Loader EFI EFI Platform Drivers EFI Drivers Framework Drivers Platform Drivers EFI Drivers Compatibility Support Module Compatibility Support Module Driver Execution Environment Pre-EFI Initiialization (PEI) Pre-EFI Modules Architectural Protocols Hardware Specific Foundations DXE Foundation PEI Foundation Hardware Hardware System Block Diagram

The Framework Directory Tree8.x code base • Framework • Application • Bus • Chipset • BearLake - MemoryInit • Blackford - MemoryInit • ESB2 • IntelIch - ICHX - SmBus • SMC • CPU • CSM • GUID • Include • Library • Platform • IntelDpg – Bearlake Pei – Dxe - Platform • IntelEsg – StarLake Pei – Dxe - Platform • IntelSSG • Bearlake - Build • StarLake - Build • Ppi • Protocol • Tools

Minimal porting job to run EFI Shell Porting SEC • Reset Fetches Code from FLASH • Enables Flat Protected Mode Execution • SEC Enables Temp Memory • Data and Stack Cached • Enables Execution of C Code • Transfers Control to PEI Foundation

Minimal porting job to run EFI Shell 0xFFFF_FFFF System ROM (16 MB) System FLASH (512 KB) Framework Code and Data Stored Here 0xFFF8_0000 SEC Maps Unused Region as Temporary Memory 0xFF00_0000 Temp Memory 0xFEF0_0000 Local APIC 0xFEE0_0000 0xFED0_0000 I/O APIC 0xFEC0_0000 0xZZZ0_0000 PCI Resources 0xYYY0_0000 Low Top Of Memory System Memory 0x0000_0000 Temporary Memory

Minimal porting job to run EFI Shell SEC phase • Currently SEC phase is where the Reset vector will start • \Platform\$(PLATFORM_SOUTH_PATH)\Common\Sec\Ia32\ResetVec.asm • \Platform\$(PLATFORM_SOUTH_PATH)\Common\Sec\Ia32\Flat32.asm

Minimal porting job to run EFI Shell PEI Phase • The PEI phase’s purpose is to: • Determine the boot mode • Perform low-level initialization of the platform • Discover and initialization main memory • Invoke recovery if desired • Transfer control to DXE or S3 waking vector

Minimal porting job to run EFI Shell PEI Phase Overall Initialization • Two PEIMs contain the majority of the platform’s initialization code : Platform\$(SOUTH_PLATFORM_PATH)\Pei\Platform\Stage1 Platform\$(SOUTH_PLATFORM_PATH)\Pei\Platform\Stage2 • The Platform Stage1 PEIM module does the platform initialization according to platform policy or board layout. Stage1 focuses on ICH related platform initialization, such as ICH GPIO initialize, since GPIO usage and initialize value is according to board layout design. • The Platform Stage2 PEIM module does the platform initialization according to platform policy or board layout. Platform Stage2 focuses on MCH related platform initialization, such as onboard Graphics enable/disable.

Minimal porting job to run EFI Shell Platform Specifics in Platform.h \Platform\$(PLATFORM_SOUTH_PATH)\Common\Pei\Platform\Platform.h • Memory DIMM SMBUS address • Firmware Hub GPIO base address and recovery jumper number • ICH ACPI base address, ICH GPIO base address, SIO base address, ICH RCBA base address • Early resource address such as AC97 audio memory mapped IO base address, ICH SMBUS base address, ICH IDE base address. • ICH GPIO mappings • PEI memory usage • ICH ACPI timer related settings such as resolution, address, and max value.

Minimal porting job to run EFI Shell GPIO Initialization • PEIM for ICH GPIO initialization • Table - mIchGpioInitTable

Minimal porting job to run EFI Shell Code Example FILE: Platform\ \$(PLATFORM_SOUTH_PATH)\ Common\Pei\Platform\Stage1\IchInit.c static const ICH_GPIO_DEV mIchGpioInitTable [] = { // Register OFFSET,Value // 0/1 - Native function/GPIO GPIO_USE_SEL, GPIO_USE_SEL_VAL, GPIO_USE_SEL2, GPIO_USE_SEL2_VAL, // 0/1 - Output/Input GPIO_IO_SEL, GPIO_IO_SEL_VAL, GPIO_IO_SEL2, GPIO_IO_SEL2_VAL, // 0/1 - Active High/Low GPIO_INV, GPIO_INV_VAL };

Minimal porting job to run EFI Shell GPIO Values The table allows you to define the register offset and value that is needed to program the GPIO’s. You can set them up for input/output/tri-state and set the high/low values using the following defines: GPIO_USE_SEL – which GPIO’s to program GPIO_IO_SEL – which direction GPIO_INV – switch High/Low state(setting) These values – GPIO_USE_SEL, GPIO_IO_SEL, and GPIO_INV are defined in the file: \Platform\$(PLATFORM_SOUTH_PATH)\Common\Pei\Platform\Platform.h

Minimal porting job to run EFI Shell ICH Initialization • Power-on ICH initialization is performed in PEI to: • Initialize the system buses (LPC, PCI, SMBUS) • Turn-off the watchdog timer • Program the interrupt pins • Other miscellaneous chipset initialization needed prior to memory detection • This initialization is performed in the file: Platform\ $(PLATFORM_SOUTH_PATH)\Pei\Platform\Stage1\IchInit.c • ICH address constants and additional ICH constants are declared in the file: Platform\ $(PLATFORM_SOUTH_PATH)\Pei\Platform\Platform.h • Platform component initialization based on user setup preferences is performed later in the DXE ICH initialization. • Resetting of the ICH is performed in the file: Chipset\IntelIch\IchX\IchInit\Pei\IchReset.c

Minimal porting job to run EFI Shell Super I/O Initialization • Power-on Super I/O initialization is performed in the file: • Platform\($(PLATFORM_SOURCE_PATH)\Pei\Platform\Stage1\SioInit.c • Devices connected to the LPC bus (e.g. fans, floppy) component initialization is performed later in the DXE Super I/O initialization

Minimal porting job to run EFI Shell PCI Routing • PCI IRQ routing table is required by some legacy OSes • DXE driver that perform PCI devices routing • Platform\$(PLATFORM_SOUTH_PATH)\Common\Dxe\LegacyBios\platform.c • Table – PirqTableHead

PIRQ Table Code Example in File: Platform\$(PLATFORM_SOUTH_PATH)\Common\Dxe \LegacyBios\platform.c EFI_LEGACY_PIRQ_TABLE PirqTableHead = { {0x52495024,00,01,0000,00,00,0000,0x8086, 0x122e,00000000,00,00,00,00,00,00,00, 00,00,00,00,00}, { // Memory Controller devices // DEFINE_PCI_ROUTINE (0, 1, PIRQA, PIRQB, PIRQC, PIRQD, 0, 0), // PEG graphics port DEFINE_PCI_ROUTINE (1, 0, PIRQA, PIRQB, PIRQC, PIRQD, 0x7, 0xFF), // PEG slot DEFINE_PCI_ROUTINE (0, 2, PIRQA, 0, 0, 0, 0, 0), // On-board graphics DEFINE_PCI_ROUTINE (0, 3, PIRQA, PIRQB, PIRQC, 0, 0, 0), // HECI . . .

PCI IRQ routing in the ACPI Tables Example in File: Platform\$(PLATFORM_SOUTH_PATH)\Common\Dxe\AcpiTables\asl\OnBoardPrt.asi It contains the internal PCI devices and onboard PCI devices IRQ routing information. Generally, all internal PCI devices with ICH or MCH should be listed. For example, USB, IDE, SATA and AC97 controllers in ICH and graphics controller in MCH

Minimal porting job to run EFI Shell Flash ROM • Implement EFI_FIRMWARE_VOLUME_ BLOCK_PROTOCOL • Enables Variable Write Services • Initializes platform specific flash device • Platform\Generic\RuntimeDxe\FvbServices\<Platform> • FWBlockService.c • Possible functions for FWH or SPI access • EnableFvbWrites ( ) • EnablePlatformFvb ( ) • PlatformGetFvbWriteBase ( ) • SetPlatformFvbLock ( )

Minimal porting job to run EFI Shell SM Bus SMBus • PEIM for ICH SMBus initialize • Chipset\IntelIch\IchX\Smbus IchSmbus.c • Functions to provide a standard way to access SMBus • SmbusExecute ( ) • SmbusIoRead ( ) • SmbusIoWrite ( )

Minimal porting job to run EFI Shell DXE IPL • Shadow DXE IPL in permanent memory • To allow sharing of decompression algorithm with DXE • Allocate 128KB stack for DXE • Create HOBs • Decompression protocol passed as HOB • Firmware Volumes • Passed in HOB • Handle S3 transition • Switch Stacks to call DXE Main

Minimal porting job to run EFI Shell SM Bus Initialize System Memory • PEIM that performs system memory initialization • Chipset\<Chipset> • Memory detection • PEI_DUAL_CHANNEL_DDR_MEMORY_CONTROLLER_PPI • Reset • RowInfo • GetMemoryMap • DetectMemory • ConfigureMemory • Memory clock control • PEI_DUAL_CHANNEL_DDR_CLOCK_GENERATOR_PPI • Capabilities • GetFrequency • SetFrequency

Minimal porting job to run EFI Shell Integrating Memory Init Code • MRC directory Chipset\<Chipset>\MemoryInit • The file MemoryInit.Inf describes the Memory Reference code contained within its description (.dsc) file. • After calling the entry to this memory init routine and successfully exiting, the memory should be ready to use. It builds HOBs to describe the memory address space and their attributes. • Some of the HOB information that is produced by the MRC: • S3 Memory • SMRAM Descriptor HOB • Memory Descriptor HOB • T-size configuration setup option (variable)

Minimal porting job to run EFI Shell SM Bus PEI Modules CPU PEIM Platform Init and CPU I/O DXE IPL PEIM Generic Starts DXE Foundation PCI Configuration PEIM PCAT Uses I/O 0xCF8, 0xCFC Stall PEIM PCAT Uses 8254 Timer Status Code PEIM Platform Debug Messages SMBus PEIM South Bridge SMBus Transactions Memory Controller PEIMs North Bridge Read SPD, Init Memory Motherboard PEIM Platform FLASH Map, Boot Policy

Minimal porting job to run EFI Shell PPI Example typedef EFI_STATUS (EFIAPI *PEI_SMBUS_PPI_EXECUTE_OPERATION) ( IN EFI_PEI_SERVICE **PeiServices, IN struct EFI_PEI_SMBUS_PPI *This, IN EFI_SMBUS_DEVICE_ADDRESS SlaveAddress, IN EFI_SMBUS_DEVICE_COMMAND Command, IN EFI_SMBUS_OPERATION Operation, IN BOOLEAN PecCheck, IN OUT UINTN *Length, IN OUT VOID *Buffer ); typedef struct { PEI_SMBUS_PPI_EXECUTE_OPERATION Execute; PEI_SMBUS_PPI_ARP_DEVICE ArpDevice; } EFI_PEI_SMBUS_PPI;

Minimal porting job to run EFI Shell PEIM Pseudo Code #define SMBUS_R_HD0 0xEFA5 #define SMBUS_R_HBD 0xEFA7 EFI_PEI_SERVICES *PeiServices; SMBUS_PRIVATE_DATA *Private;UINT8 Index, BlockCount *Length; UINT8 *Buffer; BlockCount = Private->CpuIo.IoRead8 ( *PeiServices,Private->CpuIo,SMBUS_R_HD0); if (*Length < BlockCount) { return EFI_BUFFER_TOO_SMALL; } else { for (Index = 0; Index < BlockCount; Index++) { Buffer[Index] = Private->CpuIo.IoRead8 ( *PeiServices,Private->CpuIo,SMBUS_R_HBD); } }

Minimal porting job to run EFI Shell What Are Architectural Protocols • Typically functions that isolate platform specific hardware (e.g. real-time clock) • Provide support for boot services and runtime services • Low level protocols that support DXE APIs (e.g. Boot and Runtime services) • Directly called by DXE core

Minimal porting job to run EFI Shell DXE Architectural Protocols Watchdog Generic Uses Timer-based Events Monotonic Counter Generic Uses Variable Services Runtime Generic Platform Independent CPU Platform Processor DXE Driver BDS Platform Platform Policy and TSL phase Timer PCAT Uses 8254 Timer Metronome PCAT Uses 8254 Timer Reset PCAT I/O 0xCF9 Real Time Clock PCAT I/O 0x70-0x71 Security Platform Platform Specific Authentication Status Code Platform Debug Messages Variable Platform Depends on FLASH Map

Minimal porting job to run EFI Shell DXE Drivers Consuming Architectural Protocols • Host bridge driver • Chipset\PcatCompatible\SimplePciHostBridge\Dxe • ICH initialize driver • Chipset\IntelIch\IchX\IchxInit\Dxe • IDE controller driver • Chipset\IntelIch\IchX\IdeController\Dxe • SMBus DXE driver • Chipset\IntelIch\IchX\Smbus\Dxe • Super I/O • Chipset\<SuperIO Vendor>\Dxe

Minimal porting job to run EFI Shell NT Emulation Timer Arch Protocol EFI_STATUS TimerDriverSetTimerPeriod ( IN EFI_TIMER_ARCH_PROTOCOL *This, IN UINT64 TimerPeriod ) { . . . gWinNt->EnterCriticalSection (&mNtCriticalSection); mTimerPeriod = TimerPeriod; mCancelTimerThread = FALSE; gWinNt->LeaveCriticalSection (&mNtCriticalSection); mNtLastTick = gWinNt->GetTickCount (); mNtTimerThreadHandle = gWinNt->CreateThread ( NULL, 0, NtTimerThread, &mTimer, 0, &NtThreadId); . . . }

Minimal porting job to run EFI Shell Itanium Timer Arch Protocol EFI_STATUS TimerDriverSetTimerPeriod ( IN EFI_TIMER_ARCH_PROTOCOL *This, IN UINT64 TimerPeriod ) { . . . mTimerCount = (mCpuFrequency * TimerPeriod) / NUMBER_OF_100NS_IN_A_SECOND; SetupItm (mTimerCount); // mov loc2 = ar.itc;; // add loc2 = loc2, in0;; // mov cr.itm = loc2 // srlz.d;; ItcInterruptControl (TRUE, TIMER_VECTOR_NUMBER); // mov loc2 = in1 // mov loc3 = 0x1 // mov loc4 = pr // cmp.eq p6,p7 = in0,r0;; // // (p7) dep loc2 = r0,loc2,16,1;; // Clear mask to enable intr // (p6) dep loc2 = loc3,loc2,16,1;; // Set mask to disable intr // // mov cr.itv = loc2;; // srlz.d;; // mov pr = loc4,0x1ffff . . . }

Minimal porting job to run EFI Shell XScale Timer Arch Protocol EFI_STATUS TimerDriverSetTimerPeriod ( IN EFI_TIMER_ARCH_PROTOCOL *This, IN UINT64 TimerPeriod ) { UINT64 Count; UINT32 Data; . . . Count = DivU64x32 (MultU64x32 (TimerPeriod, OST_CRYSTAL_FREQ) + 5000000, 10000000, NULL); mCpuIo->Mem.Read (mCpuIo,EfiWidthUint32,OSCR_BASE_PHYSICAL,1,&Data); Data += (UINT32)Count; mCpuIo->Mem.Write (mCpuIo,EfiWidthUint32,OSMR0_BASE_PHYSICAL,1,&Data); mCpuIo->Mem.Read (mCpuIo,EfiWidthUint32,OIER_BASE_PHYSICAL,1,&Data); Data |= (UINT32)1; mCpuIo->Mem.Write (mCpuIo,EfiWidthUint32,OIER_BASE_PHYSICAL,1,&Data); mCpuIo->Mem.Read (mCpuIo,EfiWidthUint32,ICMR_PHYSICAL,1,&Data); Data |= (UINT32)(1 << SA_OST0_IRQ_No); mCpuIo->Mem.Write (mCpuIo,EfiWidthUint32,ICMR_PHYSICAL,1,&Data); . . . }

Minimal porting job to run EFI Shell 8254 Based Timer Arch Protocol EFI_STATUS TimerDriverSetTimerPeriod ( IN EFI_TIMER_ARCH_PROTOCOL *This, IN UINT64 TimerPeriod ) { UINT64 Count; UINT8 Data; . . . Count = DivU64x32 (MultU64x32(119318, (UINTN) TimerPeriod) + 500000, 1000000, NULL); Data = 0x36; mCpuIo->Io.Write(mCpuIo,EfiCpuIoWidthUint8,TIMER_CONTROL_PORT, 1, &Data); mCpuIo->Io.Write(mCpuIo,EfiCpuIoWidthFifoUint8,TIMER0_COUNT_PORT,2,&Count); mLegacy8259->EnableIrq (mLegacy8259, Efi8259Irq0, FALSE); . . . } Different Implementations Same Protocol Interface

Minimal porting job to run EFI Shell Serial Terminal Console Services BDS / EFI Shell Virtual Console Simple Input Protocol Simple Text Output Protocol Physical Console Simple Input Protocol Simple Text Output Protocol Serial I/O Protocol ISA I/O Protocol Super I/O PCI I/O Protocol PCI Root Bridge I/O Protocol PCI Host Bridge Resource Allocation Protocol ISA ACPI Protocol

Minimal porting job to run EFI Shell Serial Terminal Console Drivers BDS / EFI Shell Generic Console Splitter Generic Generic Terminal ISA Serial PCAT ISA Bus Generic Super I/O PCI Bus Generic Platform Specific Policy Console Platform Platform Work with Chipset Vendor PCI Root Bridge North Bridge Work with Chipset Vendor PCI Host Bridge North Bridge ISA ACPI Super I/O Work with Super I/O Vendor

Minimal porting job to run EFI Shell DXE Driver for Console Services • Console Splitter Driver • Edk\Sample\Universal\Console\ConSplitter\Dxe • Graphics Console Driver • Edk\Sample\Universal\Console\GraphicsConsole\Dxe • Terminal Driver • Edk\Sample\Universal\Console\Terminal\Dxe • UGA Driver (optional) • Chipset\<Vendor>\Uga\Dxe

Minimal porting job to run EFI Shell Porting SummaryDo Minimum to Run EFI Shell Status Code PEI Platform Memory Controller PEI North Bridge SMBUS PEI South Bridge Motherboard PEI Platform Security DXE Platform SM Bus Status Code DXE Platform Variable DXE Platform Console Platform DXE Platform PCI Root Bridge DXE North Bridge PCI Host Bridge DXE North Bridge ISA ACPI DXE Super I/O

Further Information • Documents Directory on CD • Framework Mini PortingGuide • FrameworkTechPortingRef • FrameworkPortingList

Back up Back Up

2009 release Centrino Mobile Technology platform • Porting example • New form footprint no longer North / South Bridge template • Core / Uncore part of the Processor • Platform Control Hub (PCH) integrated successor to MCH + ICH instead of South Bridge • Power management considerations on mobile • Silicon released as Separate UEFI reference modules • PCH Reference code • Core / Uncore CPU Reference code • ACPI • Power Management • Memory Reference code

Platform • Platform • IntelDpg – Bearlake Pei – Dxe - Platform • IntelEsg – StarLake Pei – Dxe - Platform • IntelMpg – MobilePlatform • AcpiTables • Dsdt • SsdtPtid • VaAcpiTables • Build • Include • LegacyBiosPlatform • Library • PciPlatform • PlatformSetup • SmbiosMisc ACPI Module Package

Platform Control Hub - Chipset • Chipset • IntelIch • IntelPch – Mobile Chipset (IbexPeak) • ActiveBios • Include • IoTrap • LegacyInterrup • Library • PchInit • PchSmiDispatcher • PciExpress • Ppi • Protocol • RaidRom • Reset • S3Support • SampleCOde • SataController • SerialGpio • SmartTimer • SmBus • SmmControl • Spi • Uhci • Veci

Core/Uncore IIO Elements- • CPU • UncoreCommon • AcpiTables • Guid • Include • LegacyRegion • Library • PciHostBridge • SmbiosMemory • SmmAccess • FieldUncore • Iio (Integrated I/O ) • IioInit • IioInitLib • Include • Protocol