Electronic System Level

Electronic System Level. Curso PDesigner. Agenda. Introdução Principais desafios para o projeto de SoCs IP Cores Electronic System Level (ESL) Projeto Baseado em Plataforma SystemC TLM SPIRIT Consortium PDesigner Visão geral Arquitetura Tutorial exercícios. Oportunidade.

Electronic System Level

E N D

Presentation Transcript

Electronic System Level Curso PDesigner

Agenda • Introdução • Principais desafios para o projeto de SoCs • IP Cores • Electronic System Level (ESL) • Projeto Baseado em Plataforma • SystemC TLM • SPIRIT Consortium • PDesigner • Visão geral • Arquitetura • Tutorial • exercícios

Oportunidade Circuito Integrado Especificação Cenário Design House

Cenário Circuito Integrado Especificação

Plataformas MPSoC • Utilização de múltiplos processadores SoCs • Alta performance • Baixa potência • Baixa frequência de clock • Utilização de processadores heterogêneos

Linguagens de Projeto & Tarefas Task Language Text / UML Requirements HVLs extend & accelerate the RTL design processand enable RTL designers to cross the chasm to system level design C/C++ Untimed SystemC Algorithm Exploration Transaction Level SystemC Architecture Analysis System Verilog Verification Assertions PSL/SVA VHDL Verilog RTL Design

Processor core System specification Bus core SoC Technology What is ESL? memory IP (Devices)

System specification SoC Technology What is ESL? FUNC BEH Abstraction Levels RTL GATE

System specification SoC Technology What is ESL? System FUNC Abstraction Levels BEH RTL GATE

What is ESL? UML SysML Matlab SystemVerilog SystemC Modeling Languages ESL HW SW Simulation HW SW Synthesizable

Problems UML SysML Matlab SystemVerilog SystemC Modeling Languages ESL HW SW Simulation HW SW Synthesizable Methodologies & Tools

Initiator sc_port sc_export SystemC TLM – Arquitetura Básica template < typename REQ , typename RSP > class tlm_transport_if : public virtual sc_interface { public: virtual RSP transport( const REQ & ) = 0; tlm_transport_if virtual RSP transport( const REQ & ) = 0; transport() Target transport(.) tlm_transport_if transport(.) • sc_export exports tlm_transport_if for use by outside world • RSP transport( const REQ & ) is implemented in the slave • tlm_transport_if is the tlm bidirectional blocking interface

SystemC TLM (Transaction Level Modeling) • Comunicação utilizando chamada de funções • Pontos Fortes: • Simplicidade • Rápido e compacto • Integração de modelos de hardware e software • Suporte a reuso de design e verificação de IP • Usabilidade • Transparente a: • Nível de Abstração • Diferentes arquiteturas de comunicação (barramento, NOC, ...) • Diferentes protocolos • Principais conceitos: • Fluxo de dados Unidirecional x Bidirecional • Requisições e respostas separadas • Blocking x Nonblocking • Uso de sc_port e sc_export

SPIRIT • Padrão definido por um consórcio de empresas para distribuição de IPs • Baseado em XML • Descrição de IPs independente de linguagem

Bus definition: é um objeto que descreve uma interface interface de barramento (nomes de sinais, direção, largura, uso) e as restrições que se aplicam a estes sinais. • Meta Data: é um modo que pode ser interpretado por ferramentas para se descrever diversos aspectos do projeto

Design: descreve as instâncias de um componente e as interconexões entre as instâncias. As interconexões definem as conexões ponto-a-ponto entre interfaces dos componentes. • Gerador/Configurador: são objetos executáveis utilizados para gerar os componentes ou configurá-los.

Nome da Biblioteca Nome do SoC Identificador da versão Exemplo Simples de um SoC: Design File

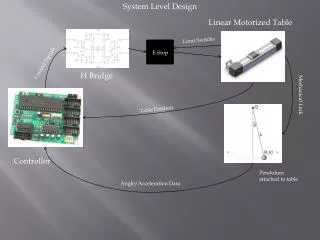

MPSoC Simulation Architecture Exploration MPSoC Modeling Processor Modeling and Integration Framework

web page SPIRIT 1.2 Framework

Modelagem de Plataformas • Modelagem gráfica de plataformas • Framework baseado no Eclipse • Ambiente Gráfico • SPIRIT 1.2 • SystemC 2.1

Simulação de Plataformas • Tela de Console com resultados da simulação • Controle de Simulação • Parar simulação

Exploração de Arquiteturas • Simulação em um único passo • Integrado ao Ambiente de modelagem de plataformas (PBuilder)

Descrição Processador Geração Processador Modelagem de Processadores • Modelagem de Processadores • ArchC 2.0 • Exporta componentes para o PBuilder

Palette Graphical Editor Platform View Properties View Modelagem de Plataformas: PBuilder

PDBuilder - Views • PEditor • Editor que possibilita a modelagem de plataformas graficamente • Componentes da biblioteca distribuídos na paleta de componentes

Mips Simple Bus Wrapper ArchC - SimpleBus Simple Bus FastMem Conexão de Componentes SimpleBus (TLM) SimpleBus (TLM) ArchC (TLM) SimpleBus (TLM)

PDBuilder - Views • Platform View • Miniatura da plataforma modelada • Outline • Lista de componentes instanciados

Properties Tabela editável com as propriedades do componente/plataforma selecionada PDBuilder - Views • Console • Mostra resultado de compilação, simulação e análise

Adicionar Componente • Remover Componente • Wrappers Biblioteca de Componentes SystemC TLM Biblioteca de Componentes: PDLibrary

TLM TLM Descrição do IP Descrição do IP Biblioteca de IPZip IPZip ( ( Wizards Wizards ) ) Componentes Distribuição de IP: IPZip

Plugin IPZip • Wizard de geração de distribuição de componente • Gera pacote de distribuição com arquivos de configuração SPIRIT a partir da descrição alto nível do componente

/******************************************************************//******************************************************************/ /* The ArchC MIPS-I functional model. */ /* Author: Sandro Rigo and Marcus Bartholomeu */ /* */ /* ... */ /* */ /* The ArchC Team */ /* Computer Systems Laboratory (LSC) */ /* IC-UNICAMP */ /* http://www.lsc.ic.unicamp.br */ /* Version: 0.75 */ /*****************************************************************/ #include "mips1_arch.H" mips1_arch::mips1_arch() : ac_arch_dec_if<mips1_parms::ac_word, mips1_parms::ac_Hword>(mips1_parms::AC_MAX_BUFFER), ac_pc("ac_pc", 0, time_step), DM_port("DM_port", 5242880), DM(*this, DM_port), RB("RB", time_step) { ac_mt_endian = mips1_parms::AC_MATCH_ENDIAN; ac_tgt_endian = mips1_parms::AC_PROC_ENDIAN; IM = &DM; APP_MEM = &DM; } class simple_bus_fast_mem : public simple_bus_slave_if , public sc_module { public: // constructor simple_bus_fast_mem(sc_module_name name_ , unsigned int start_address , unsigned int end_address) : sc_module(name_) , m_start_address(start_address) , m_end_address(end_address) { ... private: char * MEM; unsigned int m_start_address; unsigned int m_end_address; } • #include "mips1.H" • ... • const char *project_name="mips1"; • const char *project_file="mips1.ac"; • ... • int sc_main(int ac, char *av[]){ • //Platform Components • simple_bus_fast_mem mem("fast_mem",0x00,0x9fffff); • mips1 p1("p1"); • ... • //Platform Conenctions • p1.DM_port(DM_wrapper1.target_export); • ... • p1.init(); • ... • cerr << endl; • sc_start(-1); • p1.PrintStat(); • ... • cerr << endl; • return p1.ac_exit_status&& p2.ac_exit_status; • } • Cycle Accurate • Timing Estimated • Untimed • RTL • Verilog Fluxo de Distribuição do IPZip

Descrição ArchC Descrição dos Recursos (AC_ARCH) . Registradores . Memória . Estrutura de Pipeline Descrição do ISA (AC_ISA) Descrição do formato, tipo e codificação/decodifição das instruções Descrição do comportamento das instruções (C++/SystemC) Elementos da linguagem ArchC

Declaração de Instruções AC_ISA(submips){ ac_format Type_R = "%op:6 %rs:5 %rt:5 %rd:5 0x00:5 %func:6"; ac_format Type_I = "%op:6 %rs:5 %rt:5 %imm:16"; ac_instr<Type_R>add, mul; ac_instr<Type_I>lw, bne, addi; ISA_CTOR(submips) { add.set_asm("add %reg, %reg, %reg“, rd,rs,rt); add.set_decoder(op=0x00, func=0x20); lw.set_asm("lw %reg, %imm(%reg)“,rt,imm,rs); lw.set_decoder(op=0x23); ... }; }; Declaração de instruções Seqüência de decodificação